Section 3 Floating-Point Unit (FPU)

Page 102 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

3.3.2 Floating-Point Status/Control Register (FPSCR)

FPSCR is a 32-bit register that controls floating-point instructions, sets FPU exceptions, and

selects the rounding mode.

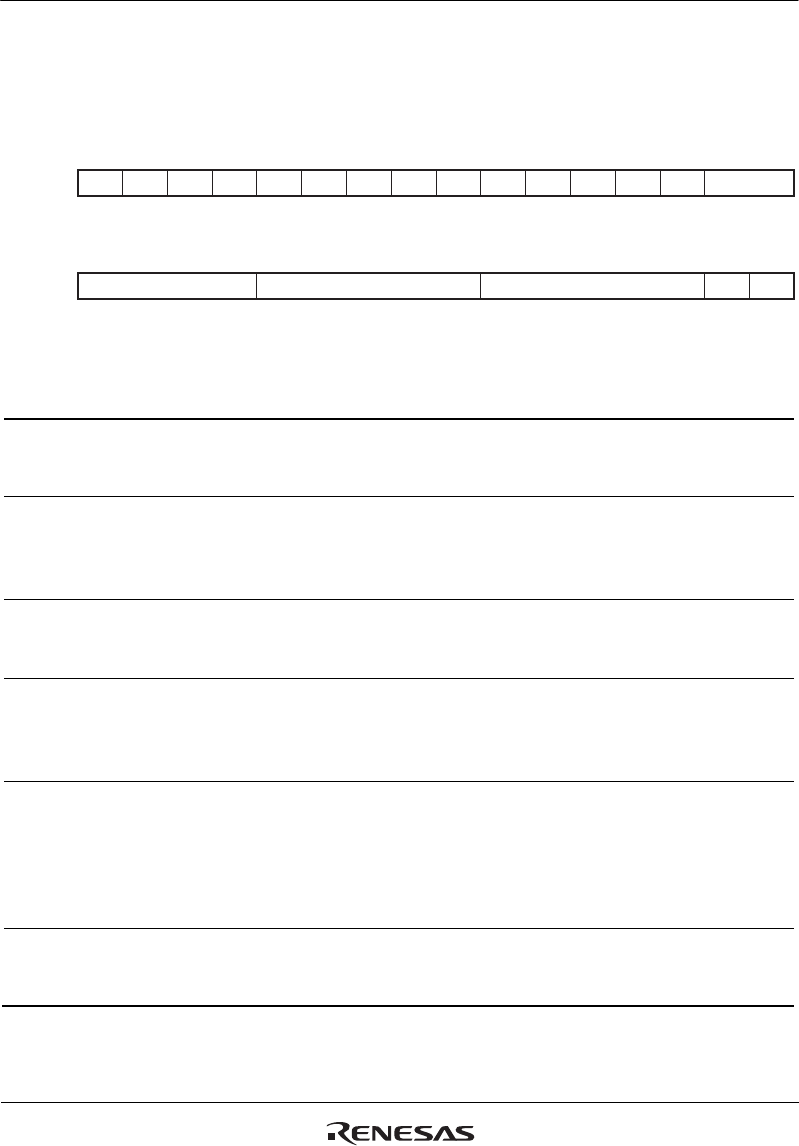

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000100

R R R R R R R R R R/W R R/W R/W R R/W R/W

0000000000000001

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

- - - - - - - - - QIS - SZ PR DN Cause

Cause Enable Flag RM1 RM0

Bit Bit Name

Initial

Value R/W

Description

31 to 23 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

22 QIS 0 R/W Nonnunerical Processing Mode

0: Processes qNaN or as such

1: Treats qNaN or as the same as sNaN (valid only

when FPSCR.Enable.V = 1)

21 0 R Reserved

This bit is always read as 0. The write value should

always be 0.

20 SZ 0 R/W Transfer Size Mode

0: Data size of FMOV instruction is 32-bits

1: Data size of FMOV instruction is a 32-bit register pair

(64 bits)

19 PR 0 R/W Precision Mode

0: Floating-point instructions are executed as single-

precision operations

1: Floating-point instructions are executed as double-

precision operations (graphics support instructions

are undefined)

18 DN 1 R Denormalization Mode (Always fixed to 1 in SH2A-

FPU)

1: Denormalized number is treated as zero