Section 35 Motor Control PWM Timer

R01UH0134EJ0400 Rev. 4.00 Page 1833 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

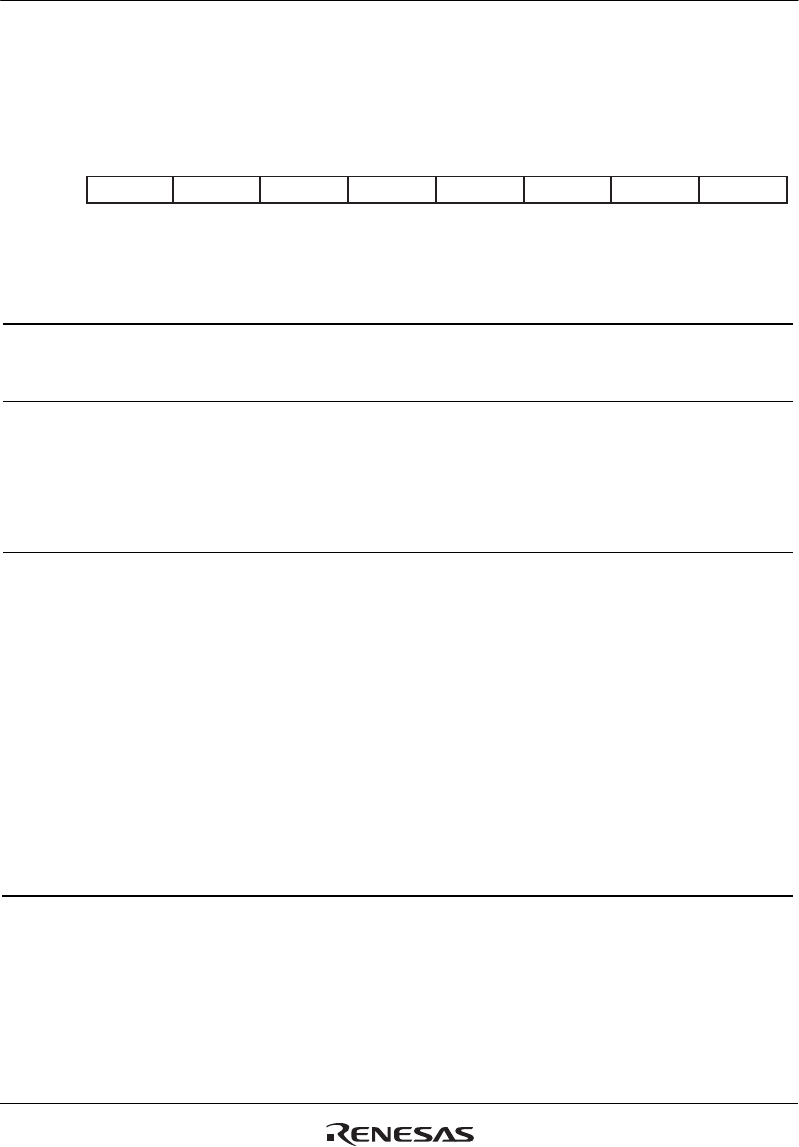

35.3.1 PWM Control Register_n (PWCR_n) (n = 1, 2)

PWCR_n performs interrupt control, starting/stopping of the counter, and counter clock selection.

It also contains a flag that indicates a compare match with the cycle register.

7

—

1

—

6

—

1

—

5

IE

0

R/W

4

CMF

0

R/(W)*

3

CST

0

R/W

0

CKS0

0

R/W

2

CKS2

0

R/W

1

CKS1

0

R/W

Bit

Bit Name

Initial Value

R/W

Bit Bit Name

Initial

Value R/W Description

7, 6 All 1 Reserved

These bits are always read as 1 and cannot be

modified.

5 IE 0 R/W Interrupt Enable

Enables or disables an interrupt request in the event of

a compare match with PWCYR_n of the corresponding

channel.

0: Interrupt disabled

1: Interrupt enabled

4 CMF 0 R/(W)* Compare Match Flag

Indicates the occurrence of a compare match with

PWCYR_n of the corresponding channel.

[Setting condition]

When PWCNT_n = PWCYR_n 1

[Clearing conditions]

When 0 is written to CMF after reading CMF = 1

When the direct memory access controller is

activated by a compare match interrupt, and the

DTA bit in DMDR of the direct memory access

controller is 1

(When the CPU is used to clear this flag by writing

0 while the corresponding interrupt is enabled, be

sure to read the flag after writing 0 to it.)