Section 28 Sampling Rate Converter

R01UH0134EJ0400 Rev. 4.00 Page 1663 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

28.4 Interrupts

This module has five interrupt sources: input data FIFO empty (IDEI), output data FIFO full

(ODFI), output data FIFO overwrite (OVF), output data FIFO underflow (UDF), and conversion

end (CEF). Table 28.11 summarizes the interrupts.

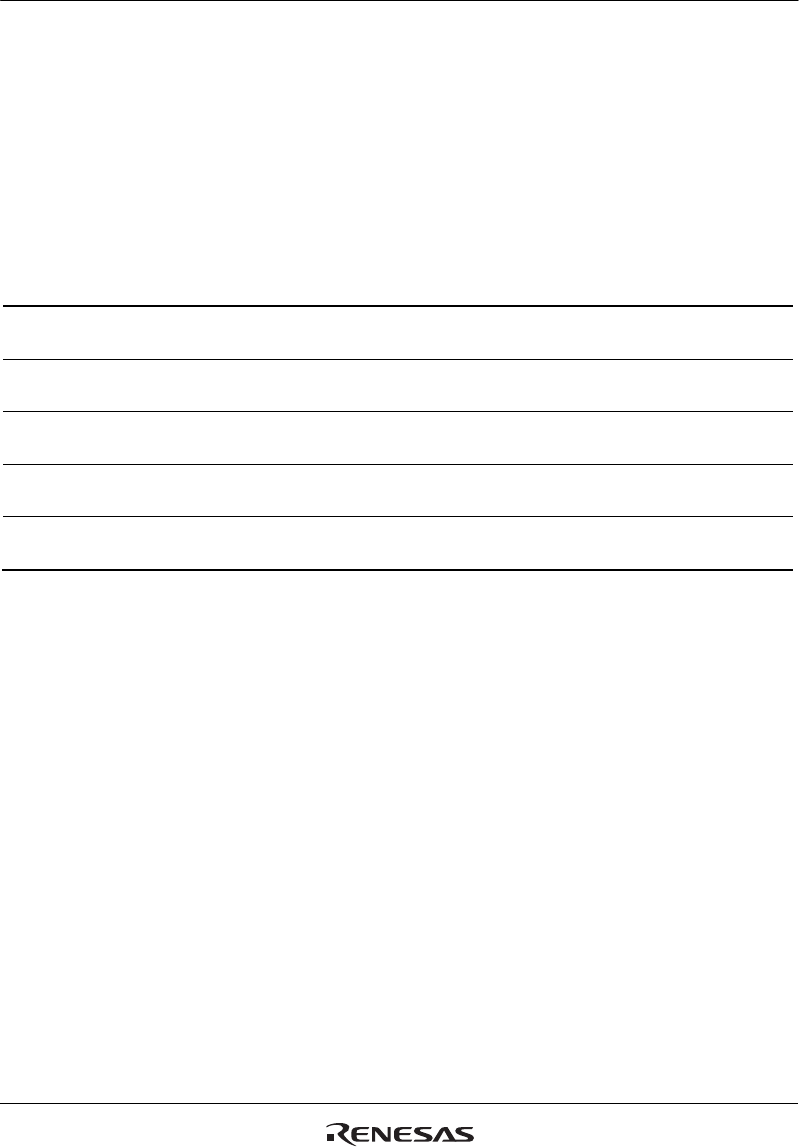

Table 28.11 Interrupt Requests and Generation Conditions

Interrupt Request Abbreviation Interrupt Condition

Direct Memory

Access Controller

Activation

Input data FIFO empty IDEI IINT = 1, IEN = 1, and

SRCEN = 1

Possible

Output data FIFO full ODFI OINT = 1, OEN = 1, and

SRCEN = 1

Possible

Output data FIFO overwrite OVF OVF = 1, OVEN = 1, and

SRCEN = 1

Not possible

Output data FIFO underflow UDF UDF = 1, UDEN = 1, and

SRCEN = 1

Not possible

Conversion end CEF CEF = 1, CEEN = 1, and

SRCEN = 1

Not possible

When the interrupt condition is satisfied, the CPU executes the interrupt exception handling

routine. The interrupt source flags should be cleared in the routine.

The IDEI and ODFI interrupts can activate the direct memory access controller when the direct

memory access controller is set to allow this. If the direct memory access controller is activated,

the interrupts from this module are not sent to the CPU. When the direct memory access controller

has written data to SRCID resulting in the number of data units in the input data FIFO exceeding

that of the specified triggering number, the IINT bit is cleared to 0. Similarly, when the direct

memory access controller has read data from SRCOD resulting in the number of data units in the

output data FIFO being less than the specified triggering number, the OINT bit is cleared to 0.