Section 11 Multi-Function Timer Pulse Unit 2

Page 572 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

(3) Interrupt Skipping in Complementary PWM Mode

Interrupts TGIA_3 (at the crest) and TCIV_4 (at the trough) in channels 3 and 4 can be skipped up

to seven times by making settings in the timer interrupt skipping set register (TITCR).

Transfers from a buffer register to a temporary register or a compare register can be skipped in

coordination with interrupt skipping by making settings in the timer buffer transfer register

(TBTER). For the linkage with buffer registers, refer to description (c), Buffer Transfer Control

Linked with Interrupt Skipping, below.

A/D converter start requests generated by the A/D converter start request delaying function can

also be skipped in coordination with interrupt skipping by making settings in the timer A/D

converter request control register (TADCR). For the linkage with the A/D converter start request

delaying function, refer to section 11.4.9, A/D Converter Start Request Delaying Function.

The setting of the timer interrupt skipping setting register (TITCR) must be done while the

TGIA_3 and TCIV_4 interrupt requests are disabled by the settings of TIER_3 and TIER_4 along

with under the conditions in which TGFA_3 and TCFV_4 flag settings by compare match never

occur. Before changing the skipping count, be sure to clear the T3AEN and T4VEN bits to 0 to

clear the skipping counter.

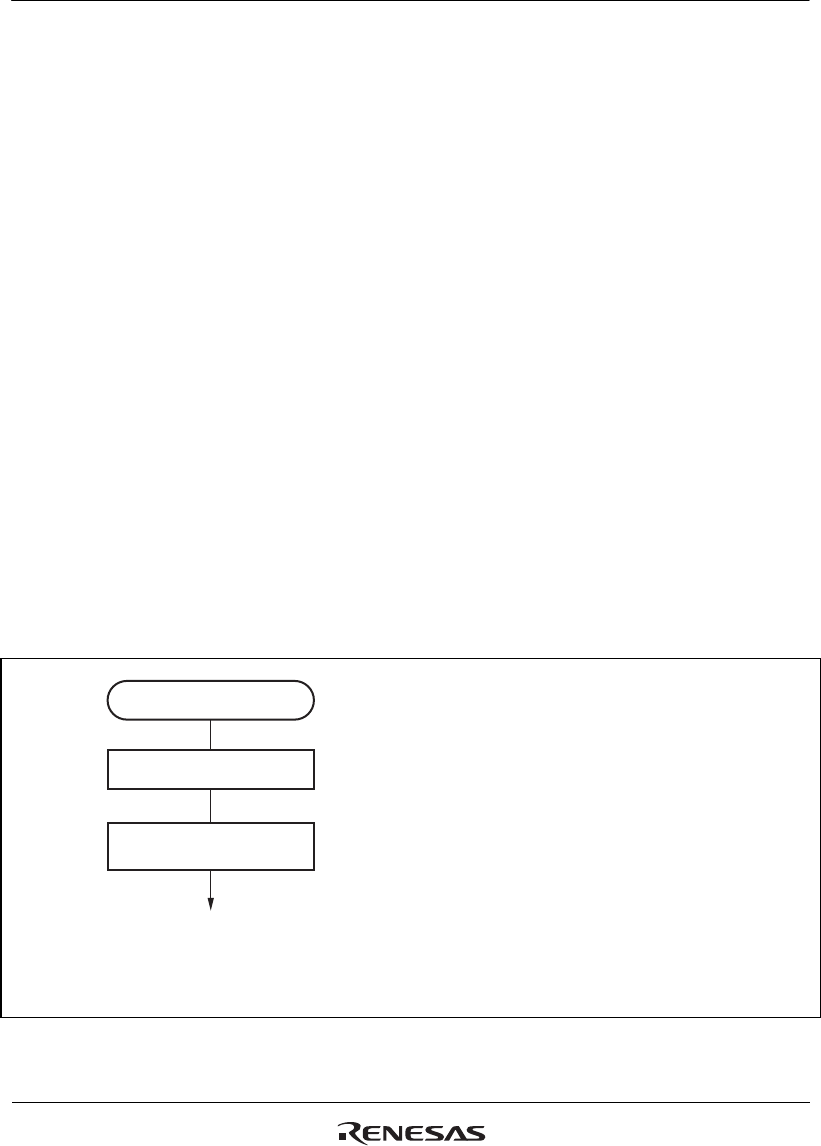

(a) Example of Interrupt Skipping Operation Setting Procedure

Figure 11.67 shows an example of the interrupt skipping operation setting procedure. Figure 11.68

shows the periods during which interrupt skipping count can be changed.

Clear interrupt skipping counter

Interrupt skipping

Set skipping count and

enable interrupt skipping

<Interrupt skipping>

[1]

[2]

[1] Set bits T3AEN and T4VEN in the timer interrupt

skipping set register (TITCR) to 0 to clear the

skipping counter.

[2] Specify the interrupt skipping count within the

range from 0 to 7 times in bits 3ACOR2 to

3ACOR0 and 4VCOR2 to 4VCOR0 in TITCR, and

enable interrupt skipping through bits T3AEN and

T4VEN.

Note: The setting of TITCR must be done while the

TGIA_3 and TCIV_4 interrupt requests are

disabled by the settings of TIER_3

and TIER_4 along with under the conditions in

which TGFA_3 and TCFV_4 flag settings by

compare match never occur.

Before changing the skipping count, be sure to

clear the T3AEN and T4VEN bits to 0 to clear

the skipping counter.

Figure 11.67 Example of Interrupt Skipping Operation Setting Procedure