Section 9 Bus State Controller

Page 294 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

9.5.2 Normal Space Interface

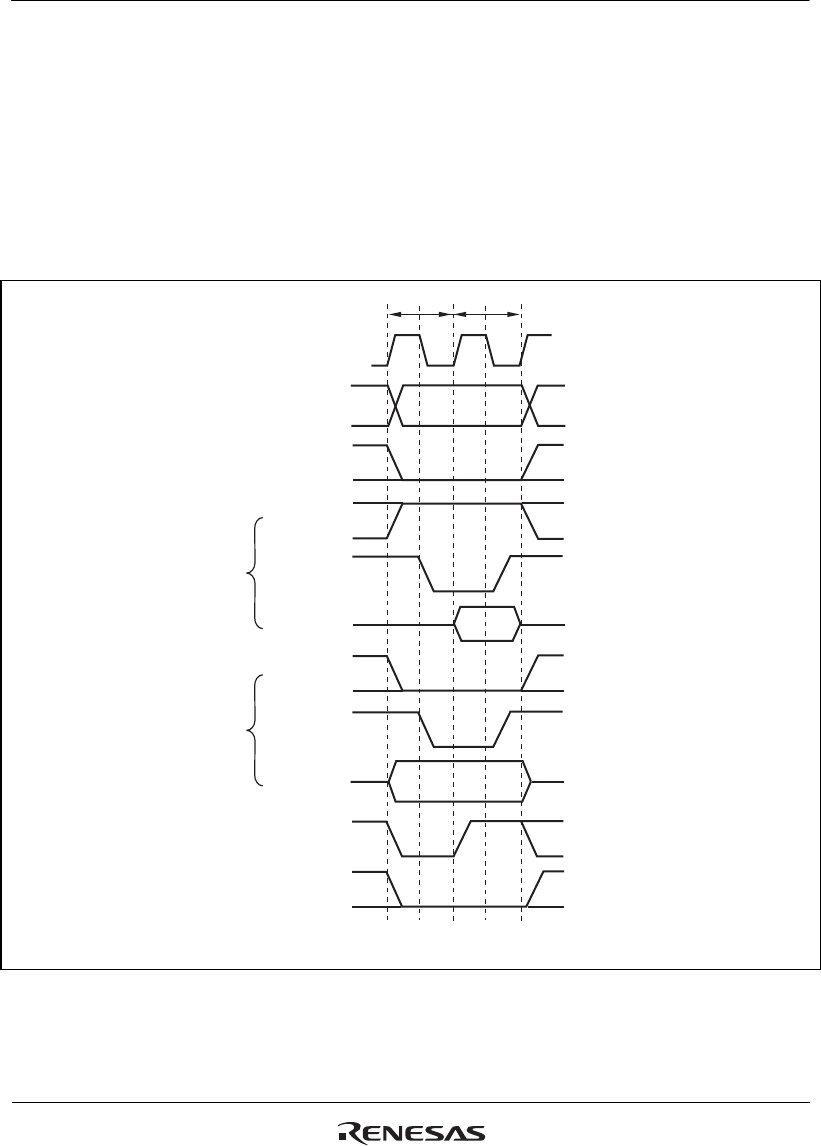

(1) Basic Timing

For access to a normal space, this LSI uses strobe signal output in consideration of the fact that

mainly static RAM will be directly connected. When using SRAM with a byte-selection pin, see

section 9.5.8, SRAM Interface with Byte Selection. Figure 9.3 shows the basic timings of normal

space access. A no-wait normal access is completed in two cycles. The BS signal is asserted for

one cycle to indicate the start of a bus cycle.

CKIO

Note: * The waveform for DACKn is when active low is specified.

A25 to A0

RD/WR

RD/WR

DACKn

CSn

T1 T2

RD

WEn

BS

D15 to D0

D15 to D0

Read

Write

*

Figure 9.3 Normal Space Basic Access Timing (Access Wait 0, Word Access)