Section 6 Exception Handling

Page 142 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

6.3 Address Errors

6.3.1 Address Error Sources

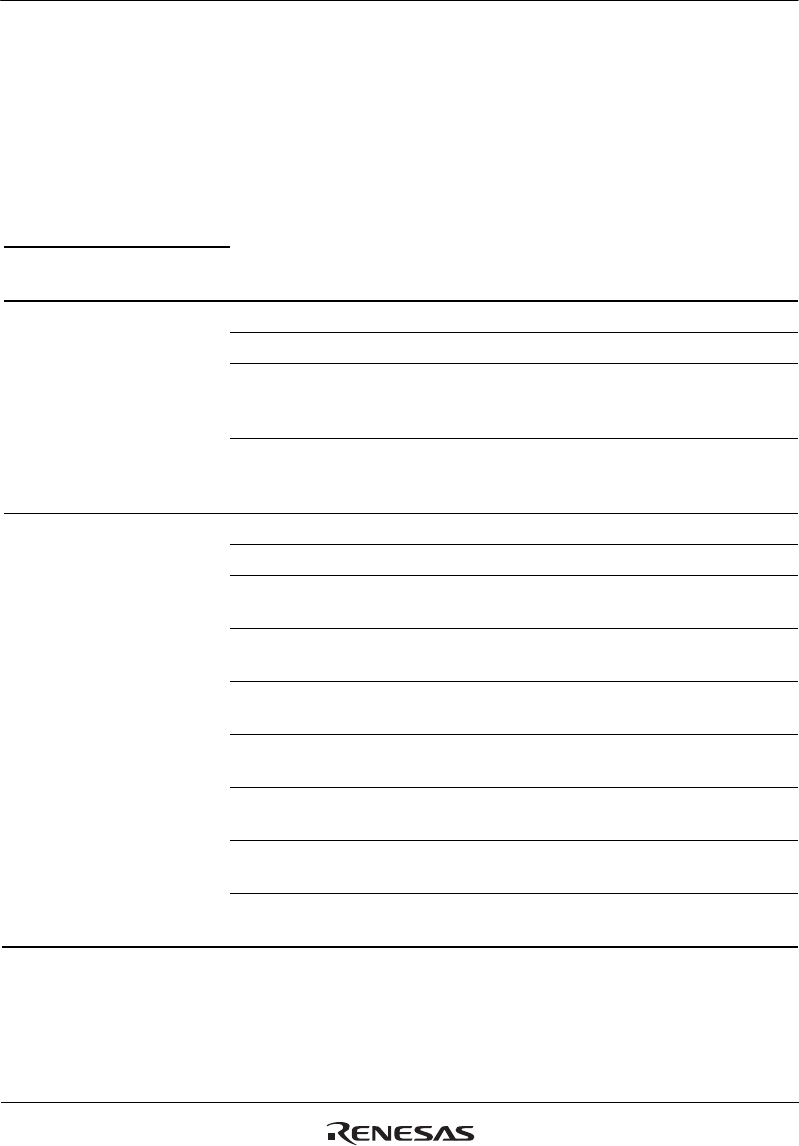

Address errors occur when instructions are fetched or data read or written, as shown in table 6.7.

Table 6.7 Bus Cycles and Address Errors

Bus Cycle

Type

Bus

Master

Bus Cycle Description Address Errors

Instruction

fetch

CPU Instruction fetched from even address None (normal)

Instruction fetched from odd address Address error occurs

Instruction fetched from other than on-chip

peripheral module space* or H'F0000000 to

H'F5FFFFFF in on-chip RAM space*

None (normal)

Instruction fetched from on-chip peripheral

module space* or H'F0000000 to

H'F5FFFFFF in on-chip RAM space*

Address error occurs

Data

read/write

CPU or

direct

memory

access

controller

Word data accessed from even address None (normal)

Word data accessed from odd address Address error occurs

Longword data accessed from a longword

boundary

None (normal)

Longword data accessed from other than a

long-word boundary

Address error occurs

Double longword data accessed from double

longword boundary

None (normal)

Double longword data accessed from other

than double longword boundary

Address error occurs

Byte or word data accessed in on-chip

peripheral module space*

None (normal)

Longword data accessed in 16-bit on-chip

peripheral module space*

None (normal)

Longword data accessed in 8-bit on-chip

peripheral module space*

None (normal)

Note: * See section 9, Bus State Controller, for details of the on-chip peripheral module space

and on-chip RAM space.