Section 2 CPU

Page 78 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

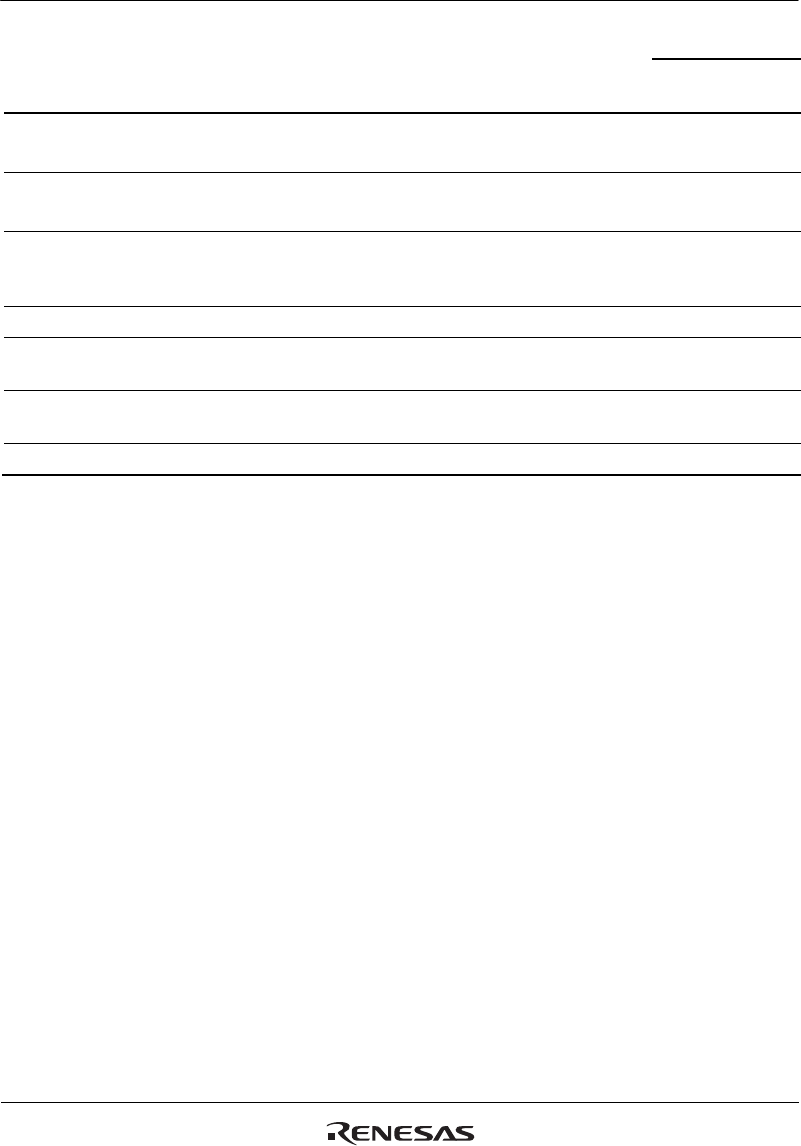

Instruction Instruction Code Operation

Execu-

tion

Cycles T Bit

Compatibility

SH2,

SH2E SH4 SH-2A

MOVU.B @(disp12,Rm),Rn 0011nnnnmmmm0001

1000dddddddddddd

(disp + Rm)

zero extension Rn

1 Yes

MOVU.W @(disp12,Rm),Rn 0011nnnnmmmm0001

1001dddddddddddd

(disp 2 + Rm)

zero extension Rn

1 Yes

NOTT 0000000001101000 ~T T 1 Oper-

ation

result

Yes

PREF @Rn 0000nnnn10000011 (Rn) operand cache 1 Yes Yes

SWAP.B Rm,Rn 0110nnnnmmmm1000 Rm swap lower 2 bytes

Rn

1 Yes Yes Yes

SWAP.W Rm,Rn 0110nnnnmmmm1001 Rm swap upper and lower

words Rn

1 Yes Yes Yes

XTRCT Rm,Rn 0010nnnnmmmm1101 Middle 32 bits of Rm:Rn Rn 1 Yes Yes Yes