Section 2 CPU

R01UH0134EJ0400 Rev. 4.00 Page 77 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

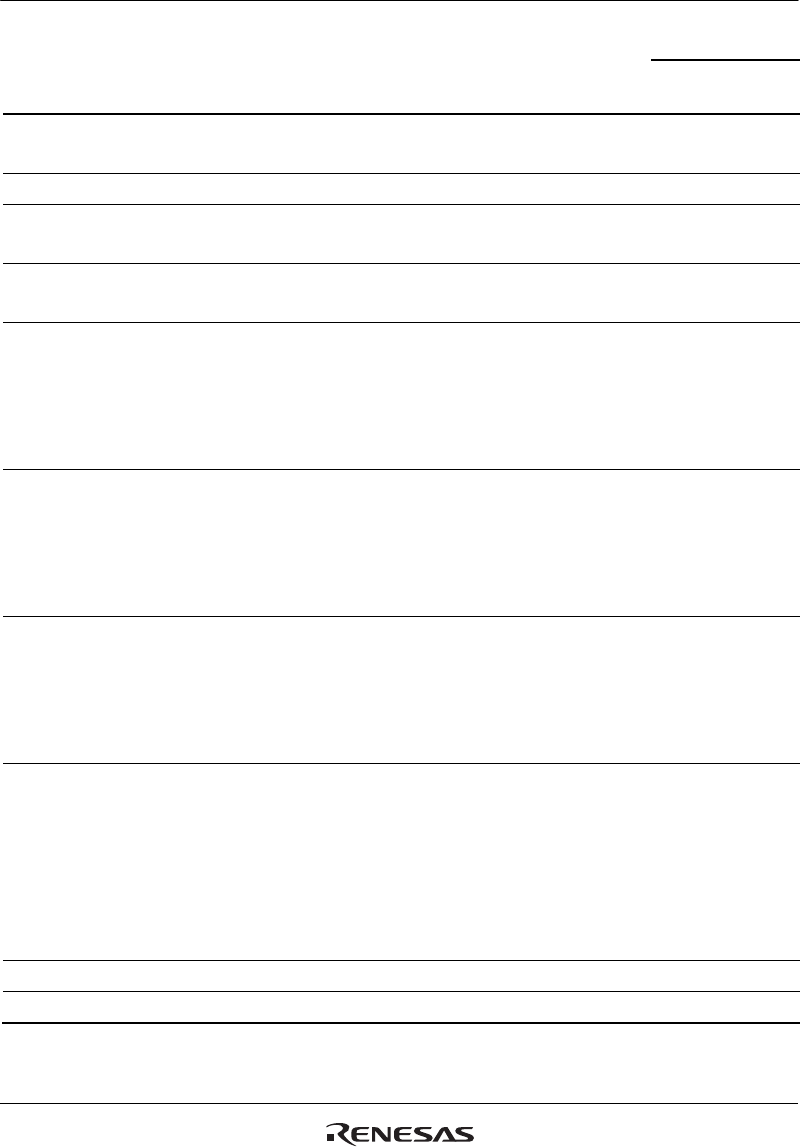

Instruction Instruction Code Operation

Execu-

tion

Cycles T Bit

Compatibility

SH2,

SH2E SH4 SH-2A

MOV.L @(disp12,Rm),Rn 0011nnnnmmmm0001

0110dddddddddddd

(disp 4 + Rm) Rn 1 Yes

MOVA @(disp,PC),R0 11000111dddddddd disp 4 + PC R0 1 Yes Yes Yes

MOVI20 #imm20,Rn 0000nnnniiii0000

iiiiiiiiiiiiiiii

imm sign extension Rn 1 Yes

MOVI20S #imm20,Rn 0000nnnniiii0001

iiiiiiiiiiiiiiii

imm << 8 sign extension

Rn

1 Yes

MOVML.L Rm,@-R15 0100mmmm11110001 R15-4 R15, Rm (R15)

R15-4 R15, Rm-1 (R15)

:

R15-4 R15, R0 (R15)

Note: When Rm = R15, read

Rm as PR

1 to 16 Yes

MOVML.L @R15+,Rn 0100nnnn11110101 (R15) R0, R15 + 4 R15

(R15) R1, R15 + 4 R15

:

(R15) Rn

Note: When Rn = R15, read

Rn as PR

1 to 16 Yes

MOVMU.L Rm,@-R15 0100mmmm11110000 R15-4 R15, PR (R15)

R15-4 R15, R14 (R15)

:

R15-4 R15, Rm (R15)

Note: When Rm = R15, read

Rm as PR

1 to 16 Yes

MOVMU.L @R15+,Rn 0100nnnn11110100 (R15) Rn, R15 + 4 R15

(R15) Rn + 1, R15 + 4

R15

:

(R15) R14, R15 + 4 R15

(R15) PR

Note: When Rn = R15, read

Rn as PR

1 to 16 Yes

MOVRT Rn 0000nnnn00111001 ~T Rn 1 Yes

MOVT Rn 0000nnnn00101001 T Rn 1 Yes Yes Yes