Section 20 Controller Area Network

R01UH0134EJ0400 Rev. 4.00 Page 1077 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

20.5 Interrupt Sources

Table 20.2 lists this module interrupt sources. These sources can be masked. Masking is

implemented using the mailbox interrupt mask registers (MBIMR) and interrupt mask register

(IMR). For details on the interrupt vector of each interrupt source, see section 7, Interrupt

Controller.

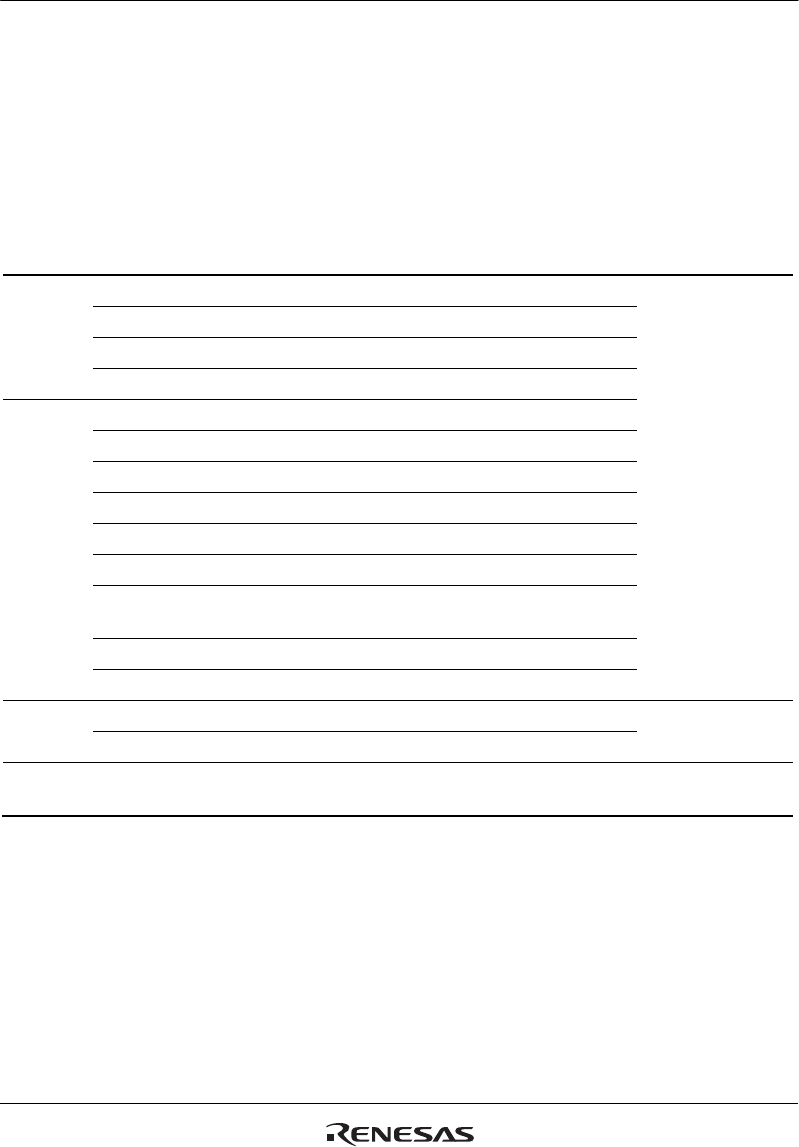

Table 20.2 Interrupt Sources

Interrupt Description Interrupt Flag DMAC Activation

ERSn*

1

Error Passive Mode (TEC 128 or REC 128) IRR5 Not possible

Bus Off (TEC 256)/Bus Off recovery IRR6

Error warning (TEC 96) IRR3

Error warning (REC 96) IRR4

OVRn*

1

Reset/halt/CAN sleep transition IRR0

Overload frame transmission IRR7

Unread message overwrite (overrun) IRR9

Start of new system matrix IRR10

TCMR2 compare match IRR11

Bus activity while in sleep mode IRR12

Timer overrun/Next_is_Gap reception/message

error

IRR13

TCMR0 compare match IRR14

TCMR1 compare match IRR15

RM0n*

1

*

2

,

RM1n*

1

*

2

Data frame reception IRR1*

3

Possible*

4

Remote frame reception IRR2*

3

SLEn*

1

Message transmission/transmission disabled

(slot empty)

IRR8 Not possible

Notes: 1. n = 0, 1

2. RM0 is an interrupt generated by the remote request pending flag for mailbox 0

(RFPR0[0]) or the data frame receive flag for mailbox 0 (RXPR0[0]). RM1 is an interrupt

generated by the remote request pending flag for mailbox n (RFPR0[n]) or the data

frame receive flag for mailbox n (RXPR0[n]) (n = 1 to 31).

3. IRR1 is a data frame received interrupt flag for mailboxes 0 to 31, and IRR2 is a remote

frame request interrupt flag for mailboxes 0 to 31.

4. The direct memory access controller is activated only by an RM0n interrupt.