Section 7 Interrupt Controller

Page 172 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

7.3.9 Bank Number Register (IBNR)

IBNR is a 16-bit register that enables or disables use of register banks and register bank overflow

exception. IBNR also indicates the bank number to which saving is performed next through the

bits BN3 to BN0.

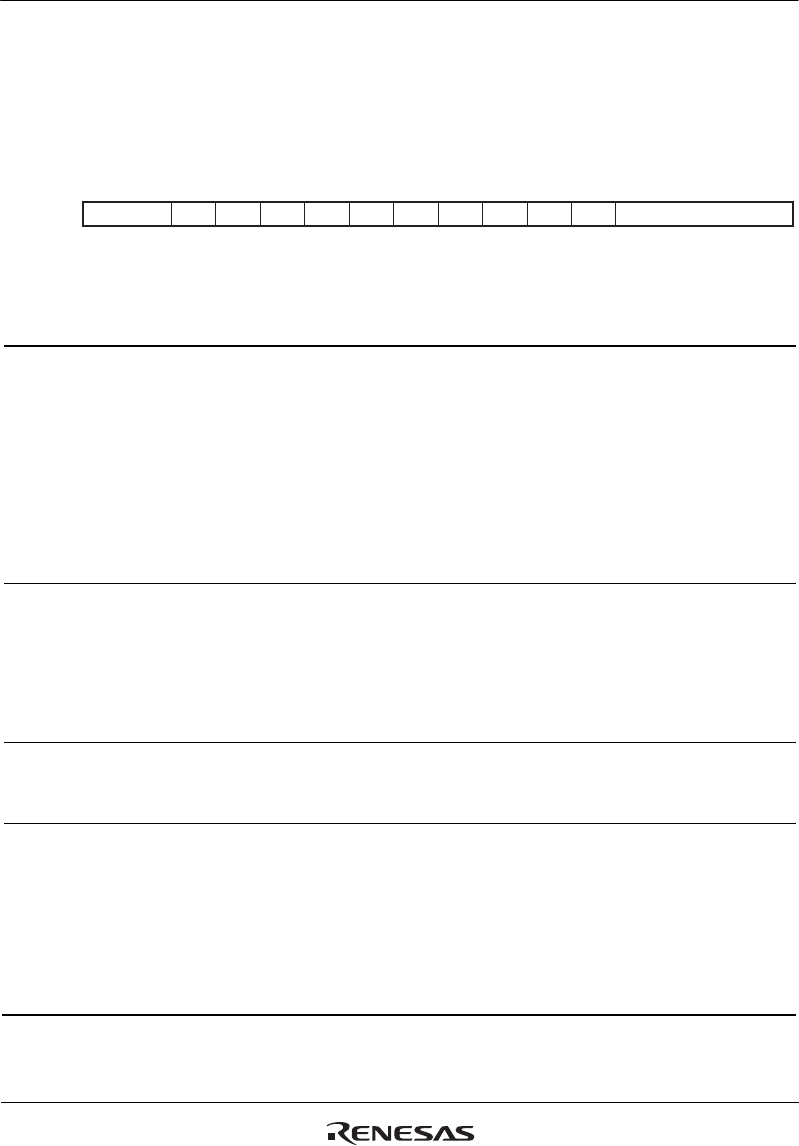

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

R/W R/W R/W R R R R R R R R R R R R R

Bit:

Initial value:

R/W:

BE[1:0] BOVE - - - - - - - - - BN[3:0]

Bit Bit Name

Initial

Value R/W Description

15, 14 BE[1:0] 00 R/W Register Bank Enable

These bits enable or disable use of register banks.

00: Use of register banks is disabled for all interrupts.

The setting of IBCR is ignored.

01: Use of register banks is enabled for all interrupts

except NMI. The setting of IBCR is ignored.

10: Reserved (setting prohibited)

11: Use of register banks is controlled by the setting of

IBCR.

13 BOVE 0 R/W Register Bank Overflow Enable

Enables of disables register bank overflow exception.

0: Generation of register bank overflow exception is

disabled

1: Generation of register bank overflow exception is

enabled

12 to 4 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

3 to 0 BN[3:0] 0000 R Bank Number

These bits indicate the bank number to which saving is

performed next. When an interrupt using register banks

is accepted, saving is performed to the register bank

indicated by these bits, and BN is incremented by 1.

After BN is decremented by 1 due to execution of a

RESBANK (restore from register bank) instruction,

restoration from the register bank is performed.