Section 38 States and Handling of Pins

R01UH0134EJ0400 Rev. 4.00 Page 2055 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

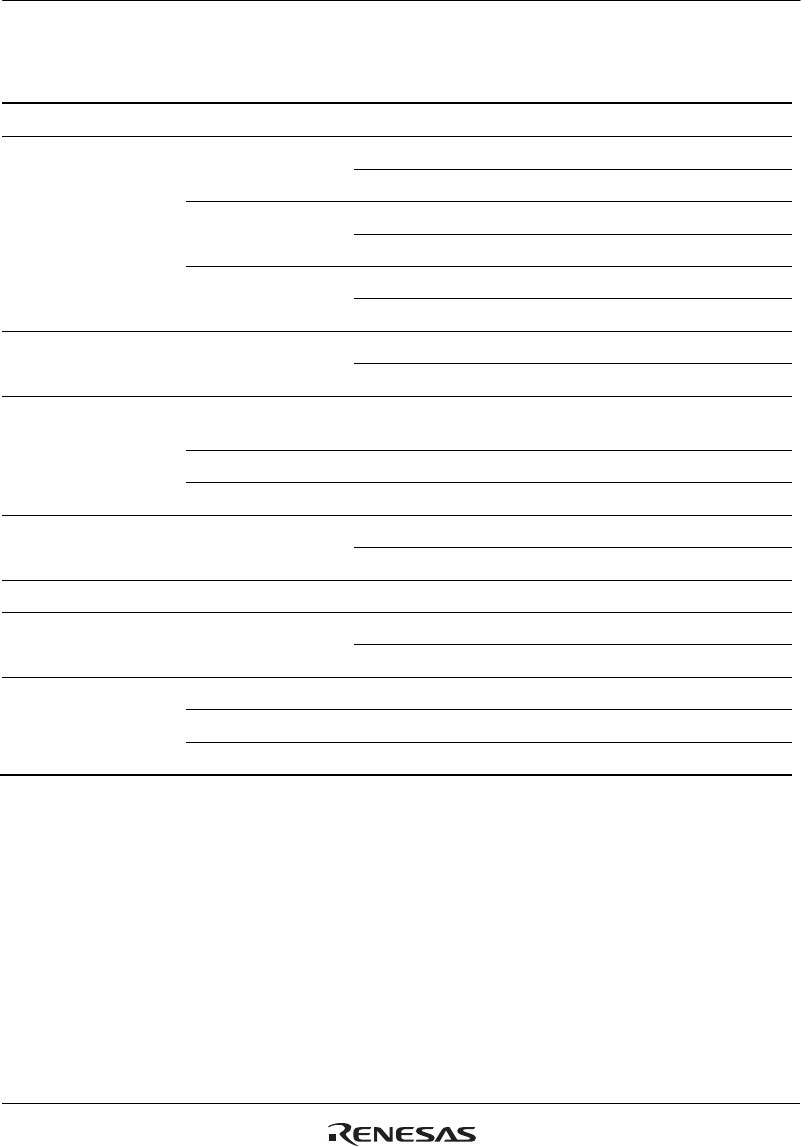

Table 38.2 Input Buffer State in Deep Standby Mode

Pin Function Pin State

Type Pin Name 1-Mbyte Version 640-Kbyte Version

Interrupt IRQ7 to IRQ4 PC8 to PC5 I/Z*

12

PG7 to PG4 Z

IRQ3, IRQ2 PE3, PE2 Z

PG11, PG10 Z I/Z*

12

IRQ1, IRQ0 PE1, PE0 Z

PJ3, PJ1 I/Z*

12

Multi-function timer

pulse unit 2

TIOC4A to TIOC4D PB16 to PB19 Z

PC5 to PC8 I/Z*

12

Serial communication

interface with FIFO

RxD7, RxD6, RxD4 to

RxD1

Z

RxD5 Z I/Z*

12

RxD0 I/Z*

12

Serial sound interface SSIRxD0 PG10 Z I/Z*

12

PK10 Z

Serial I/O with FIFO SIOFRxD Z I/Z*

12

IEBus

TM

controller IERxD PJ1 I/Z*

12

PJ5 Z

General purpose I/O

ports

PC8 to PC5 I/Z*

12

PG11, PG10 Z I/Z*

12

PJ3, PJ1 I/Z*

12

[Legend]

I: Input

O: Output

H: High-level output

L: Low-level output

Z: High-impedance

Notes: 1. Indicates the power-on reset by low-level input to the RES pin. The pin states after a

power-on reset by the user debugging interface reset assert command or the watchdog

timer overflow is the same as the initial pin states at normal operation (see section 32,

General Purpose I/O Ports).