Section 25 NAND Flash Memory Controller

R01UH0134EJ0400 Rev. 4.00 Page 1293 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

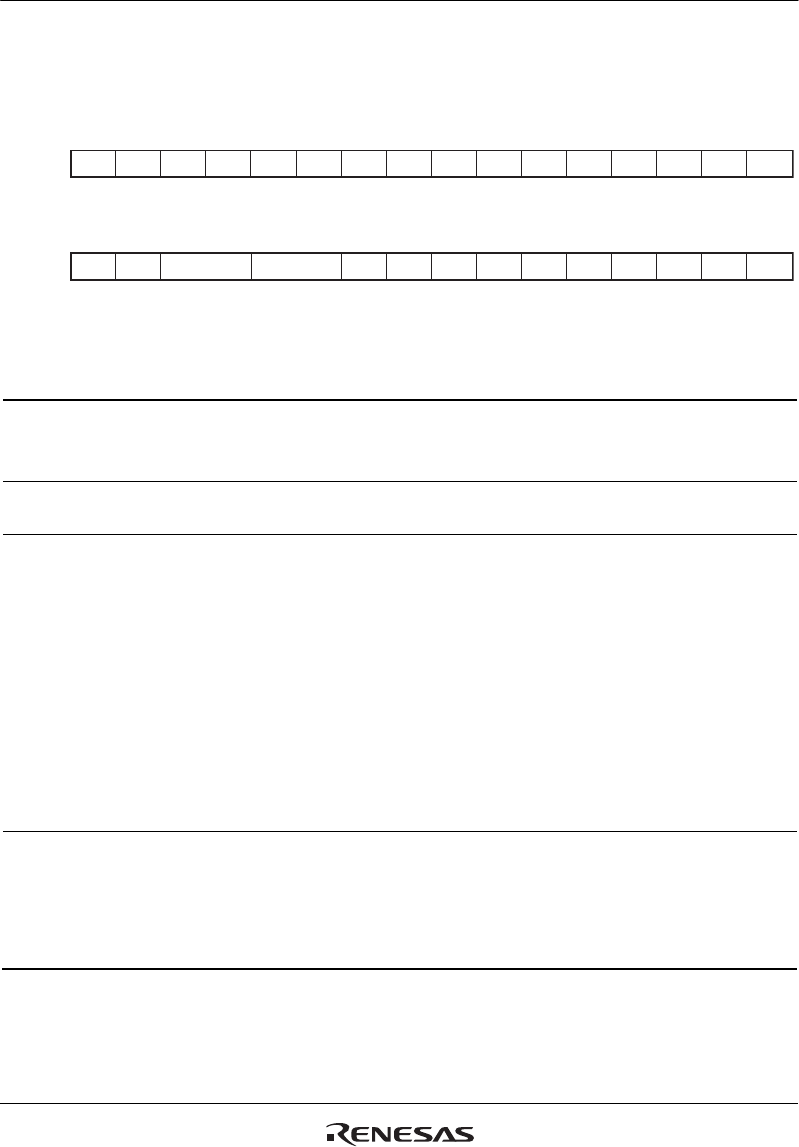

25.3.1 Common Control Register (FLCMNCR)

FLCMNCR is a 32-bit readable/writable register that specifies access mode, and other items.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit:

Initial value:

R/W:

1514131211109876543210

Bit:

Initial value:

R/W:

0000000000010000

RRRRRRR/WR/WR/WR/WR/WRRR/WR/WR

0000000000000001

R R R/W R/W R/W R/W R/W R R R R R R/W R R R

------

ECCPOS

[2]

4ECCCN

TEN

4ECCEN

4ECCCO

RRECT

BUSYON

- - SNAND

QT

SEL

-

- - ECCPOS[1:0] ACM[1:0]

NAND

WF

----

-CE---

Bit Bit Name

Initial

Value R/W Description

31 to 26 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

25 ECCPOS

[2]

0 R/W See the description of ECCPOS[1:0] at bits 13 and 12.

24 4ECCCN

TEN

0 R/W 4-Symbol ECC Error Count

Selects whether to output to the FL4ECCCNT register

the total number of errors found in the sectors that have

been read and the maximum number of errors found in

a single sector.

0: Error counting is not performed.

1: When 4-symbol ECC circuit is used, the total number

of errors found in the read sectors and the maximum

number of errors in a sector are output to

FL4ECCCNT.

Note: When this bit is set to 1, the 4ECCCORRECT bit

must be cleared to 0.

23 4ECCEN 0 R/W 4-Symbol ECC Circuit Enable

Enables the 4-symbol ECC circuit by setting this bit to 1

in sector access mode.

0: 3-symbol ECC circuit is enabled.

1: 4-symbol ECC circuit is enabled.