Section 19 Serial I/O with FIFO

R01UH0134EJ0400 Rev. 4.00 Page 945 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Bit Bit Name

Initial

Value R/W Description

3 to 0 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

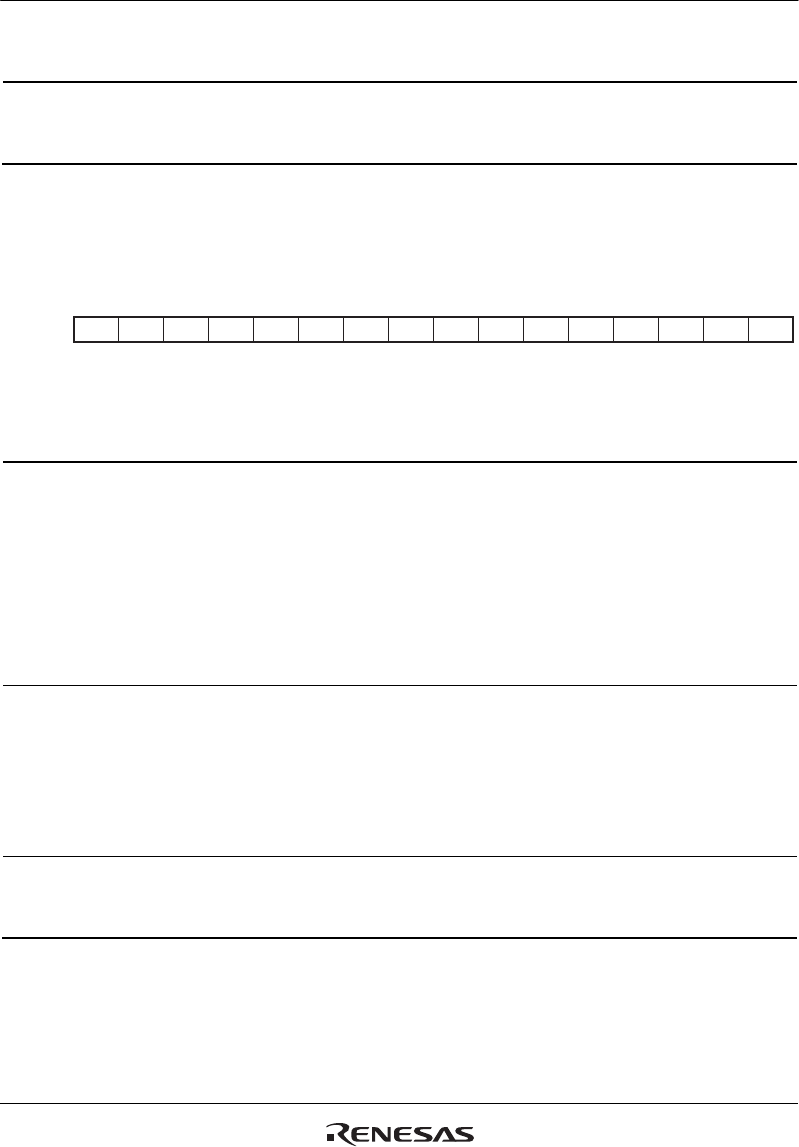

19.3.2 Control Register (SICTR)

SICTR sets the operating state for this module.

Bit:

Initial Value:

R/W:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

R/W R/W R R R R R/W R/W R R R R R R R/W R/W

SCKE FSE - - - - TXE RXE - -

-

- - - TXRST RXRST

Bit Bit Name

Initial

Value

R/W Description

15 SCKE 0 R/W Serial Clock Output Enable

This bit is valid in master mode.

0: Disables the SIOFSCK output (outputs 0)

1: Enables the SIOFSCK output

If this bit is set to 1, this module initializes the baud

rate generator and initiates the operation. At the

same time, the clock generated by the baud rate

generator is output to the SIOFSCK pin.

14 FSE 0 R/W Frame Synchronous Signal Output Enable

This bit is valid in master mode.

0: Disables the SIOFSYNC output (outputs 0)

1: Enables the SIOFSYNC output

If this bit is set to 1, this module initializes the frame

counter and initiates the operation.

13 to 10 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.