Section 11 Multi-Function Timer Pulse Unit 2

Page 612 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

11.7.18 Contention between TCNT Write and Overflow/Underflow

If there is an up-count or down-count in the T2 state of a TCNT write cycle, and

overflow/underflow occurs, the TCNT write takes precedence and the TCFV/TCFU flag in TSR is

not set.

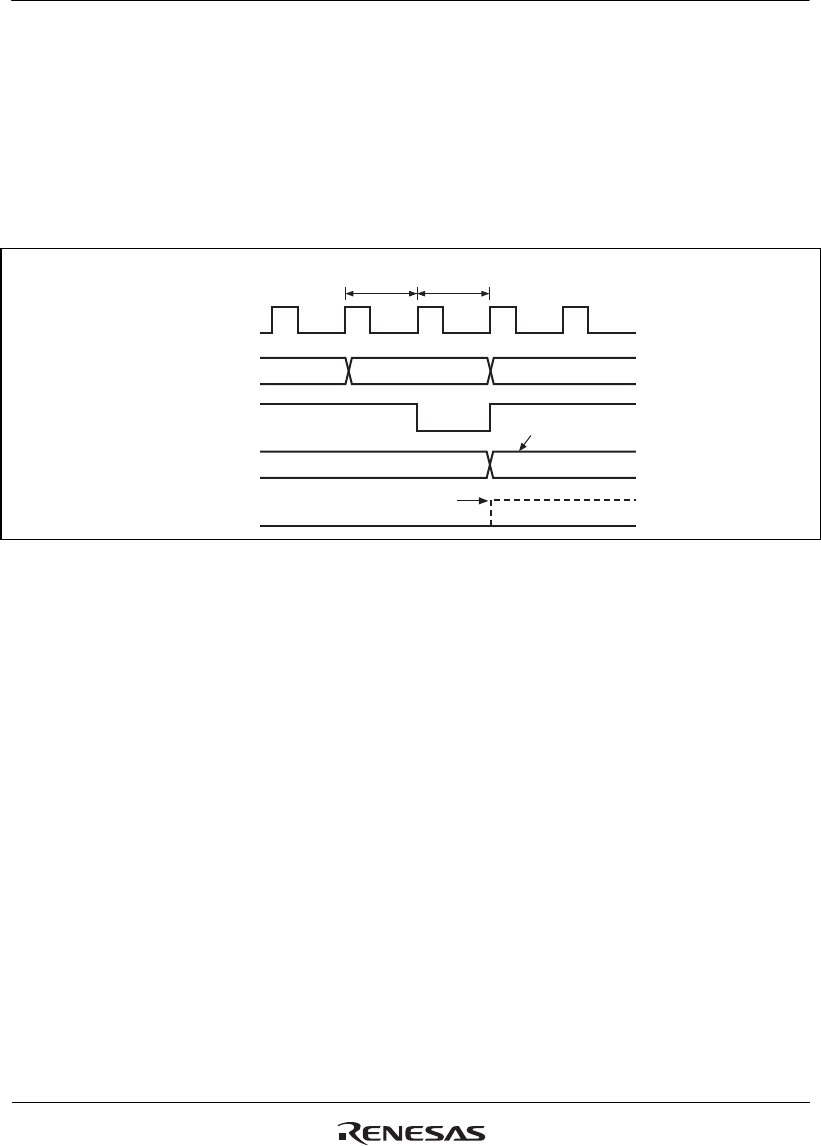

Figure 11.112 shows the operation timing when there is contention between TCNT write and

overflow.

Disabled

Write signal

Address

TCNT address

TCNT

TCNT write cycle

T1

T2

H'FFFF M

TCNT write data

TCFV flag

MPφ

Figure 11.112 Contention between TCNT Write and Overflow

11.7.19 Cautions on Transition from Normal Operation or PWM Mode 1 to Reset-

Synchronized PWM Mode

When making a transition from channel 3 or 4 normal operation or PWM mode 1 to reset-

synchronized PWM mode, if the counter is halted with the output pins (TIOC3B, TIOC3D,

TIOC4A, TIOC4C, TIOC4B, TIOC4D) in the high-level state, followed by the transition to reset-

synchronized PWM mode and operation in that mode, the initial pin output will not be correct.

When making a transition from normal operation to reset-synchronized PWM mode, write H'11 to

registers TIORH_3, TIORL_3, TIORH_4, and TIORL_4 to initialize the output pins to low level

output, then set an initial register value of H'00 before making the mode transition.

When making a transition from PWM mode 1 to reset-synchronized PWM mode, first switch to

normal operation, then initialize the output pins to low level output and set an initial register value

of H'00 before making the transition to reset-synchronized PWM mode.