Section 22 Renesas SPDIF Interface

Page 1162 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

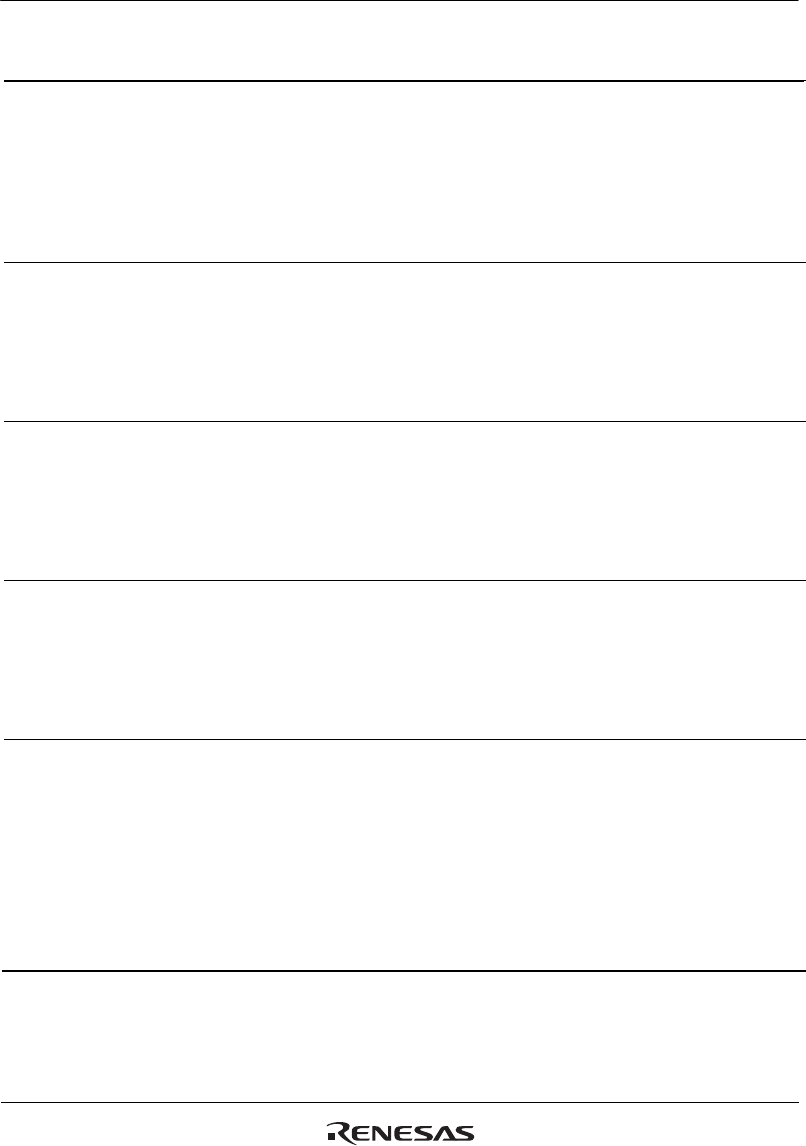

Bit Bit Name

Initial

Value R/W Description

13 UBO 0 R/WC0 User Buffer Overrun*

Sets if the receiver user buffer overruns. This bit is

cleared by writing 0 to the register. If bit REIE and bit

UBOI in the control register are set this causes an

interrupt.

0: User buffer has not overrun

1: User buffer has overrun

12 UBU 0 R/WC0 User Buffer Underrun*

Sets if the transmitter user buffer underrun. This bit is

cleared by writing 0. If bits TEIE and UBUI in the control

register are set this causes an interrupt.

0: User buffer has not underrun

1: User buffer has underrun

11 CE 0 R/WC0 Clock Error*

Sets when the clock recovery falls out of synchronization.

This bit is cleared by writing 0. If bits REIE and CREI in

the control register are set this causes an interrupt.

0: Clock recovery stable

1: Clock recovery error

10 PARE 0 R/WC0 Parity Error*

Sets when the parity checker produces a fail result. This

bit is cleared by writing 0. If bits REIE and PAEI in the

control register are set this causes an interrupt.

0: Parity check correct

1: Parity error

9 PREE 0 R/WC0 Preamble Error*

Sets when the start of word preamble fails to appear in

the correct place. This bit is cleared by writing 0. If bits

REIE and PREI in the control register are set this causes

an interrupt.

Note: Only set after a start of block preamble has

occurred.

0: Preamble is in the correct place

1: Preamble error