Section 27 Video Display Controller 3

Page 1624 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

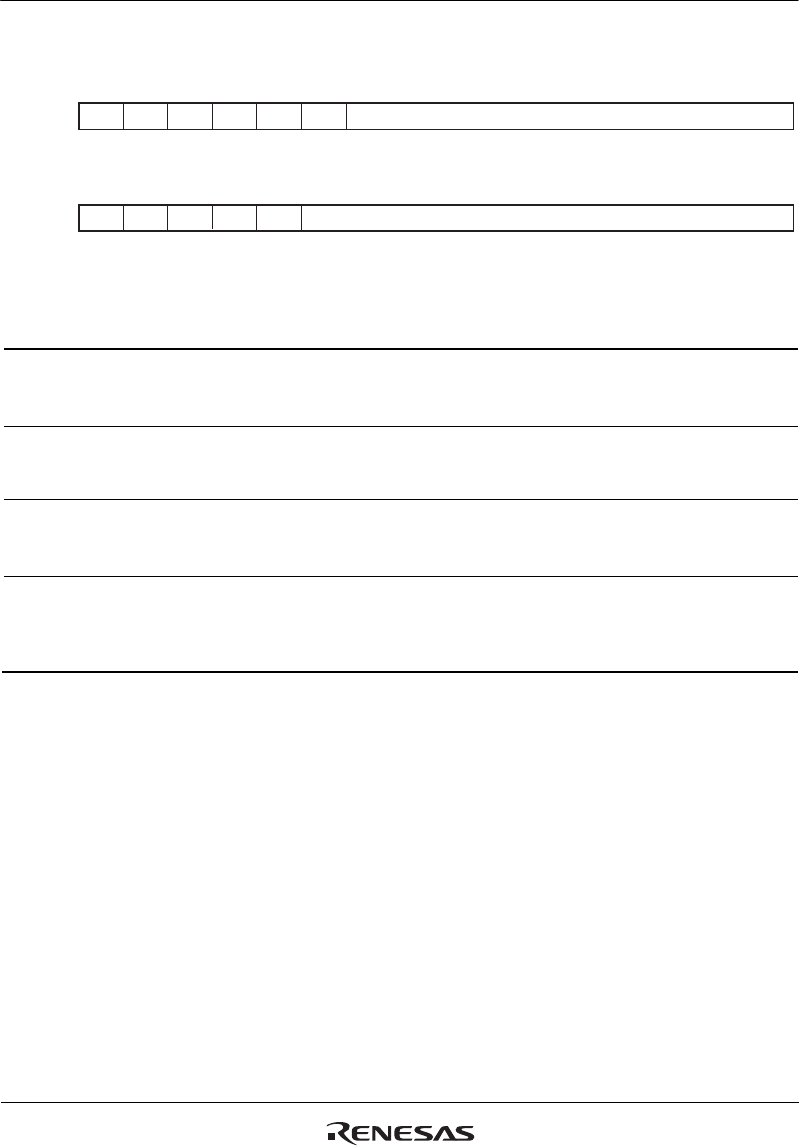

27.7.40 DE Area Start Position Register (DE_START)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

RRRRRRR/WR/WR/WR/WR/WR/WR/WR/WR/WR/W

0000000000000000

RRRRRR/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/W

- - - - - - DE_START_V[9:0]

- - - - - DE_START_H[10:0]

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

Bit Bit Name

Initial

Value R/W Description

31 to 26 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

25 to 16 DE_START_

V[9:0]

H'000 R/W These bits specify in number of lines the vertical

interval between the reference vertical sync signal

and the start of the data enable (DE) signal output.

15 to 11 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

10 to 0 DE_START_

H[10:0]

H'000 R/W These bits specify in number of panel clock cycles

the horizontal interval between the reference

horizontal sync signal and the start of the data

enable (DE) signal output.

Note: Be sure to satisfy SYN_HEIGHT > DE_HEIGHT + DE_START_V; otherwise, correct

operation is not guaranteed.

Be sure to satisfy SYN_WIDTH > DE_WIDTH + DE_START_H; otherwise, correct

operation is not guaranteed.