Section 15 Serial Communication Interface with FIFO

R01UH0134EJ0400 Rev. 4.00 Page 767 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Error handling

Clear ORER flag in SCLSR to 0

End

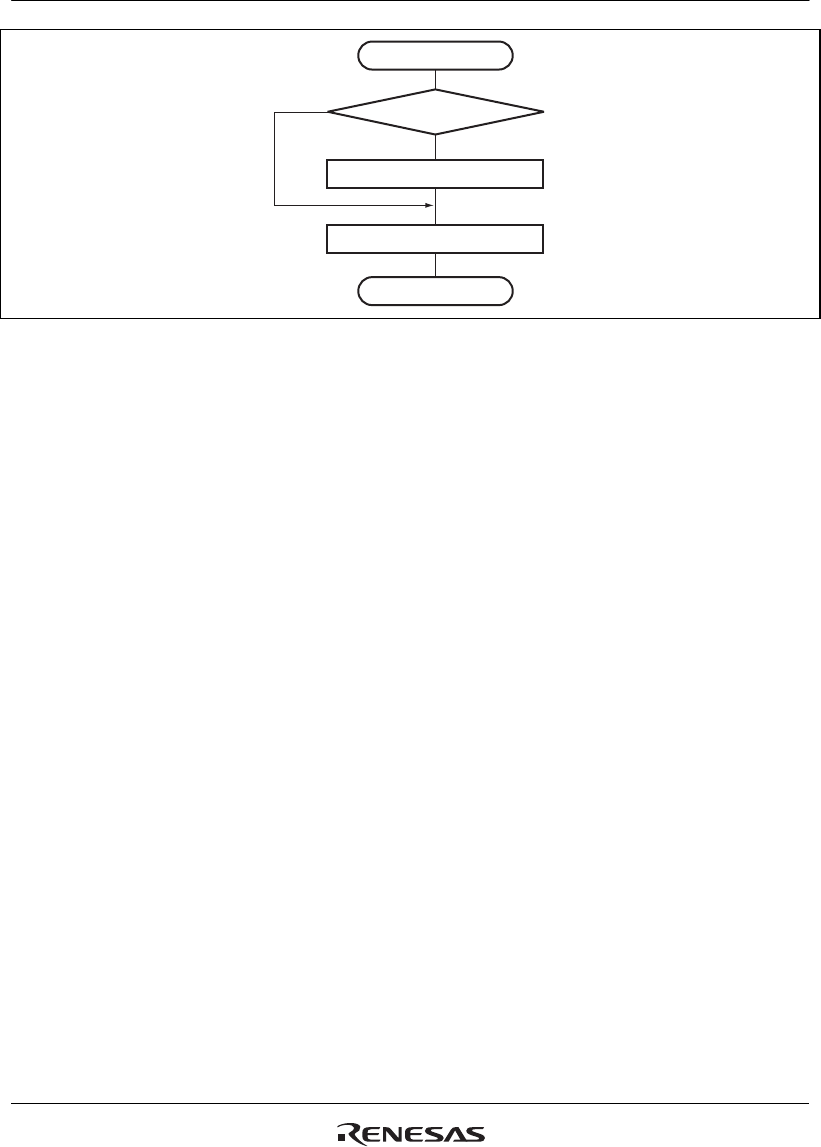

Overrun error handling

ORER = 1?

Yes

No

Figure 15.16 Sample Flowchart for Receiving Serial Data (2)

In serial reception, this module operates as described below.

1. Reception is started in synchronization with serial clock input or output.

2. Receive data is shifted into SCRSR in order from the LSB to the MSB. After the data

reception, whether the receive data can be loaded from SCRSR into SCFRDR or not is

checked. If this check is passed, the RDF flag is set to 1 and the received data is stored in

SCFRDR. If the check is not passed (overrun error is detected), further reception is prevented.

3. After setting RDF to 1, if the receive FIFO data full interrupt enable bit (RIE) is set to 1 in

SCSCR, a receive-data-full interrupt (RXI) request is generated. If the ORER bit is set to 1 and

the receive-data-full interrupt enable bit (RIE) or the receive error interrupt enable bit (REIE)

in SCSCR is also set to 1, a break interrupt (BRI) request is generated.