Section 20 Controller Area Network

Page 994 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

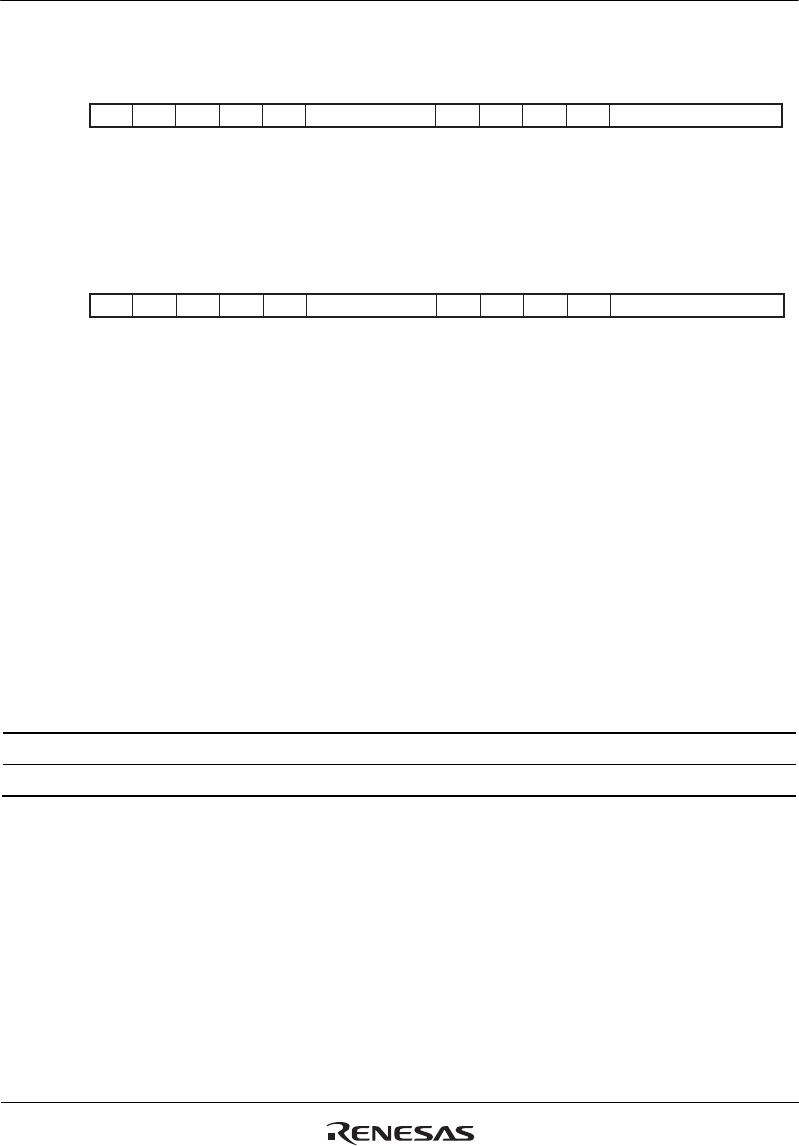

Mailbox-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0Bit:

Initial value:

R/W:

0000011100000000

RRR/W RRR/W RR/W RRRRR/W R/W R/W R/W

0 0 NMC 0 0 MBC[2:0] 0 0 0 0 DLC[3:0]

Note: MBC[1] of MB0 is always "1".

Mailbox-31 to 1

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000011100000000

RRR/W R/W R/W R/W R/W R/W RRRRR/W R/W R/W R/W

0 0 NMC ATX DART MBC[2:0] 0 0 0 0 DLC[3:0]

Bit:

Initial value:

R/W:

NMC (New Message Control): When this bit is set to '0', the Mailbox of which the RXPR or

RFPR bit is already set does not store the new message but maintains the old one and sets the

UMSR correspondent bit. When this bit is set to '1', the Mailbox of which the RXPR or RFPR bit

is already set overwrites with the new message and sets the UMSR correspondent bit.

Important: Please note that if a remote frame is overwritten with a data frame or vice versa could

be that both RXPR and RFPR flags (together with UMSR) are set for the same Mailbox. In this

case the RTR bit within the Mailbox Control Field should be relied upon.

Important: Please note that when the Time Triggered mode is used NMC needs to be set to ‘1’

for Mailbox 31 to allow synchronization with all incoming reference messages even when

RXPR[31] is not cleared.

NMC Description

0 Overrun mode (Initial value)

1 Overwrite mode