Section 11 Multi-Function Timer Pulse Unit 2

R01UH0134EJ0400 Rev. 4.00 Page 565 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

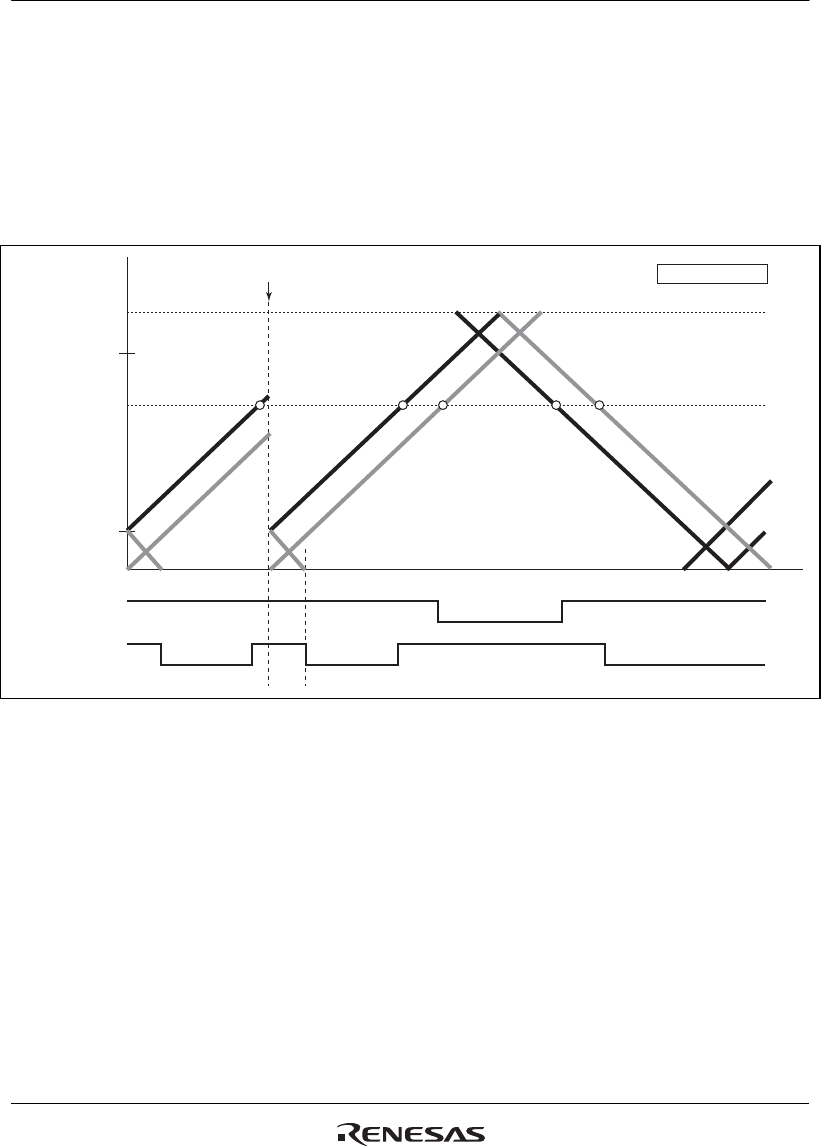

Examples of Output Waveform Control at Synchronous Counter Clearing in Complementary

PWM Mode

Figures 11.58 to 11.61 show examples of output waveform control in which this module

operates in complementary PWM mode and synchronous counter clearing is generated while

the WRE bit in TWCR is set to 1. In the examples shown in figures 11.58 to 11.61,

synchronous counter clearing occurs at timing (3), (6), (8), and (11) shown in figure 11.56,

respectively.

TGRA_3

TGRB_3

TCDR

TDDR

H'0000

Positive phase

Negative phase

Output waveform is active-low.

Synchronous clearing

TCNT_3

(MTU2)

TCNT_4

(MTU2)

Bit WRE = 1

Figure 11.58 Example of Synchronous Clearing in Dead Time during Up-Counting

(Timing (3) in Figure 11.56; Bit WRE of TWCR is 1)