Section 28 Sampling Rate Converter

Page 1640 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

28.2.1 Input Data Register (SRCID)

SRCID is a readable/writable register that is used to input the data before sampling rate

conversion. All the bits are read as 0. The data input to SRCID is stored in the 8-stage input data

FIFO. When the number of data units in the input data FIFO is 8, writing to SRCID has no effect.

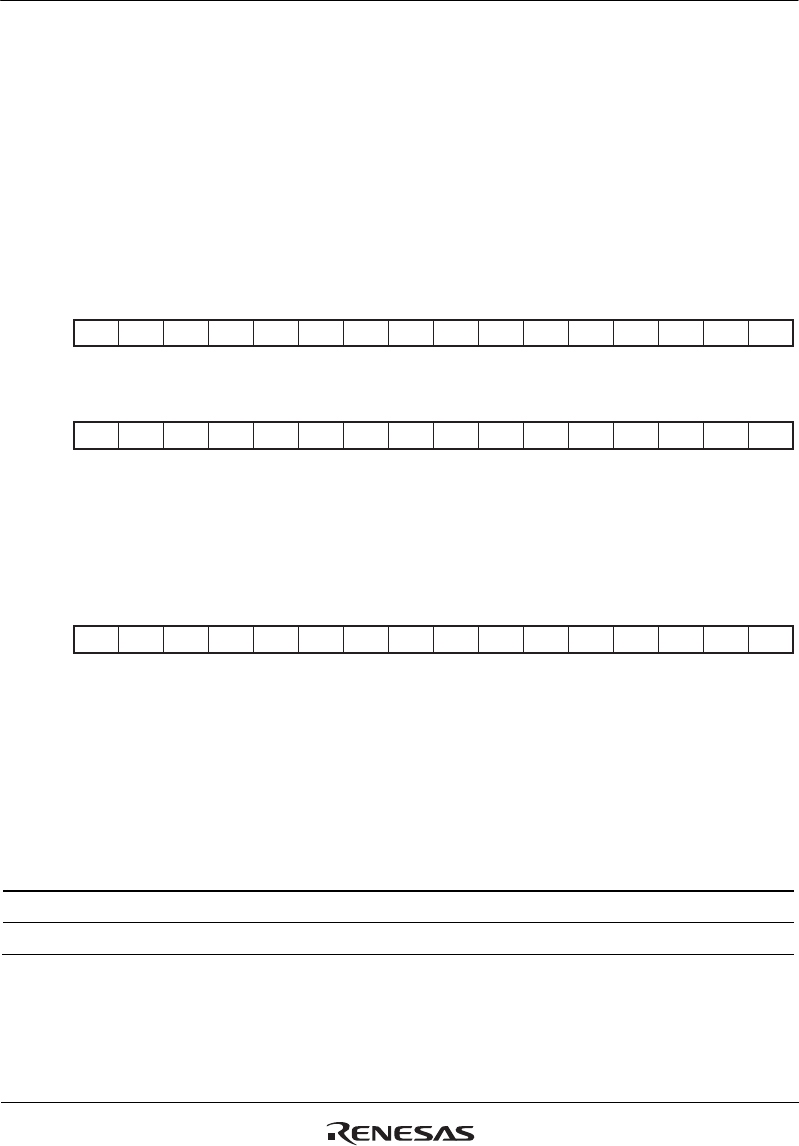

(1) Input Data Register_0 (SRCID_0)

SRCID_0 is a 32-bit register. For stereo data, bits 31 to 16 are for Lch data, and bits 15 to 0 are for

Rch data. For monaural data, data in bits 31 to 16 is valid, and data in bits 15 to 0 is invalid.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit:

Initial value:

R/W:

1514131211109876543210

Bit:

Initial value:

R/W:

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

(2) Input Data Register_1 (SRCID_1)

SRCID_1 is a 16-bit register. Monaural data in bits 15 to 0 is valid.

1514131211109876543210

Bit:

Initial value:

R/W:

0000000000000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

The data subject to sampling rate conversion is aligned differently depending on the IED bit

setting in SRCIDCTRL. Tables 28.3 and 28.4 show the relationship between the IED bit setting

and data alignment.

Table 28.3 Alignment of Data before Sampling Rate Conversion (Channel 0)

IED Lch[15:8] Lch[7:0] Rch[15:8] Lch[7:0]

0 SRCID[31:24] SRCID[23:16] SRCID[15:8] SRCID[7:0]

1 SRCID[23:16] SRCID[31:24] SRCID[7:0] SRCID[15:8]