Section 15 Serial Communication Interface with FIFO

R01UH0134EJ0400 Rev. 4.00 Page 753 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

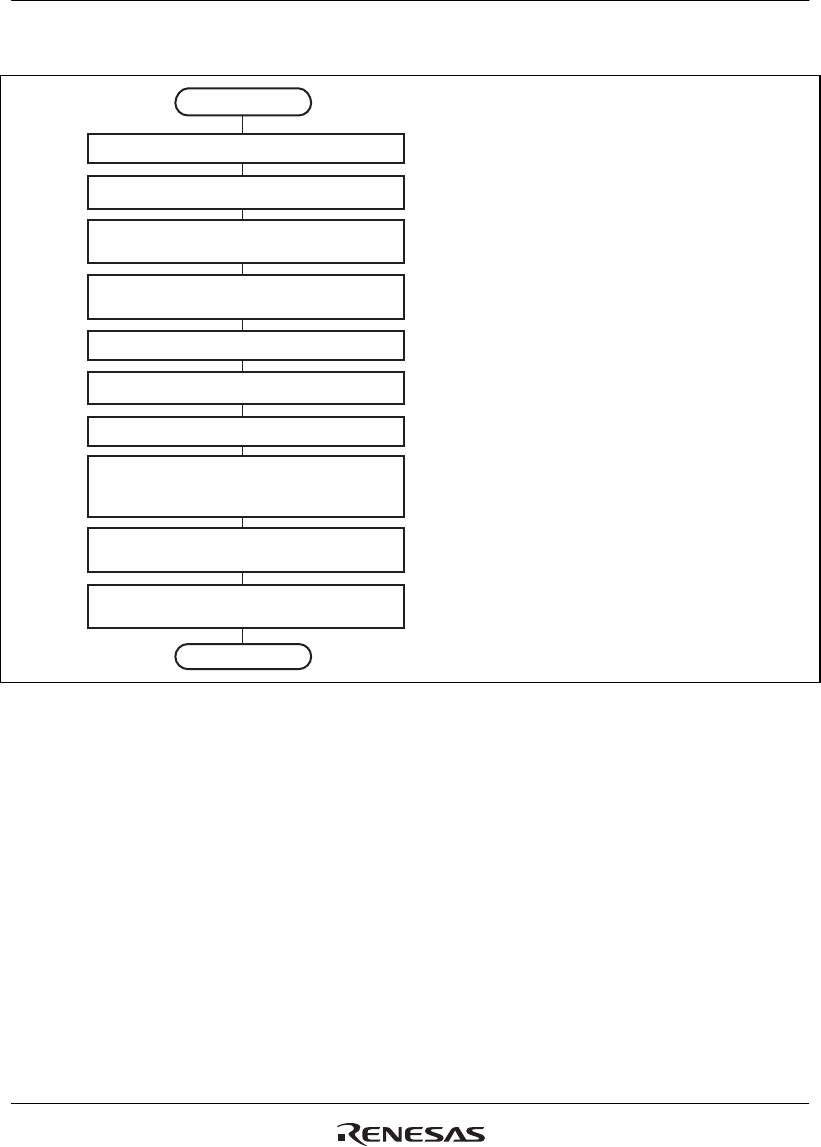

Figure 15.3 shows a sample flowchart for initialization.

Set the BGDM and ABCS bits in SCEMR

Start of initialization

Clear the TE and RE bits in SCSCR to 0

Set the TFRST and RFRST bits in SCFCR to 1

After reading flags ER, DR, and BRK in SCFSR,

and each flag in SCLSR, write 0 to clear them

Set the CKE1 and CKE0 bits in SCSCR

(leaving bits TIE, RIE, TE, and RE cleared to 0)

Set data transfer format in SCSMR

Set value in SCBRR

Set the RTRG1, RTRG0, TTRG1, TTRG0, and

MCE bits in SCFCR, and

clear TFRST and RFRST bits to 0

Set the general I/O port external pins used

SCK, TxD, RxD

Set the TE and RE bits in SCSCR to 1,

and set the TIE, RIE, and REIE bits

End of initialization

Set the clock selection in SCSCR.

Be sure to clear bits TIE, RIE, TE,

and RE to 0.

Set the data transfer format in

SCSMR.

Write a value corresponding to the

bit rate into SCBRR. (Not

necessary if an external clock is

used.)

Sets the general I/O port external pins

used. Set as RxD input at receiving

and TxD at transmission.

However, no setting for SCK pin is

required when CKE[1:0] is 00.

In the case when internal synchronous

clock output is set, the SCK pin starts

outputting the clock at this stage.

Set the TE bit or RE bit in SCSCR

to 1. Also set the RIE, REIE, and

TIE bits. Setting the TE and RE bits

enables the TxD and RxD pins to be

used.

When transmitting, the SCIF will go

to the mark state; when receiving,

it will go to the idle state, waiting for

a start bit.

[1]

[2]

[3]

[4]

[5]

[1]

[2]

[3]

[4]

[5]

Figure 15.3 Sample Flowchart for Initialization