Section 9 Bus State Controller

R01UH0134EJ0400 Rev. 4.00 Page 269 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

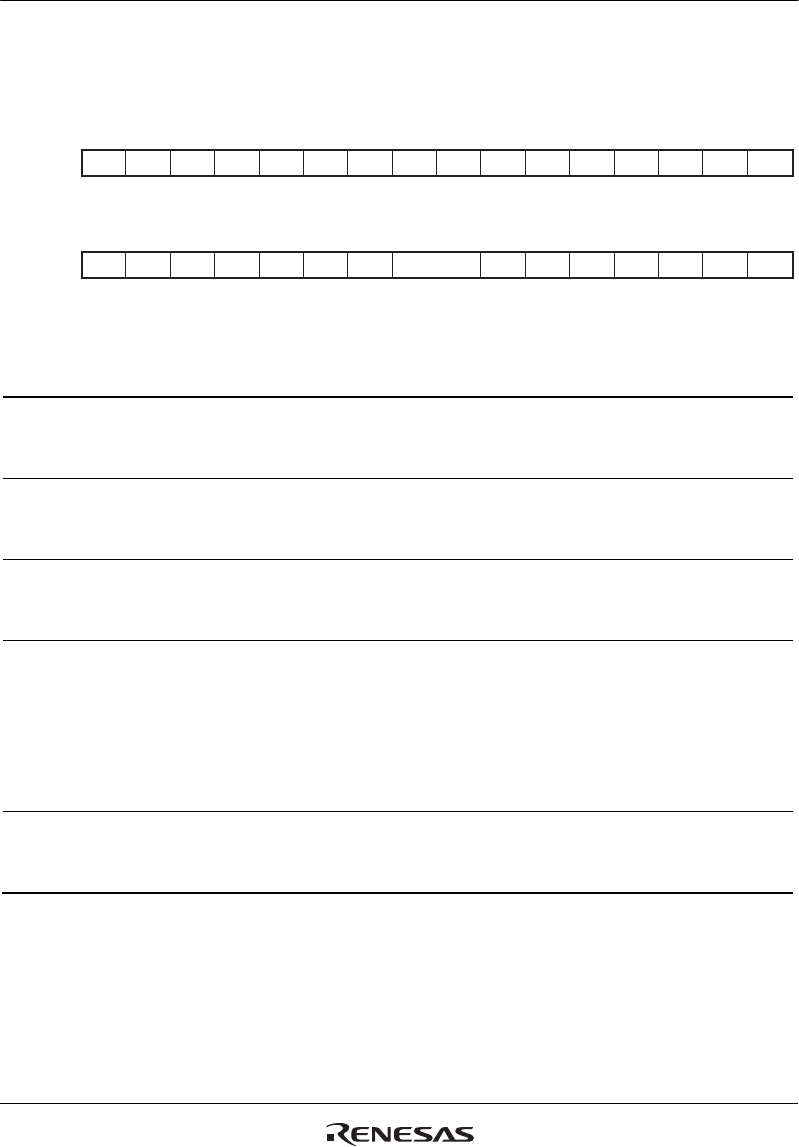

(3) SDRAM*

CS2WCR

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

RRRRRRRRRRRRRRRR

0000010100000000

RRRRRRRR/WR/WRRRRRRR

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

----------------

-------A2CL[1:0] - - - - - - -

Bit Bit Name

Initial

Value

R/W Description

31 to 11 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

10 1 R Reserved

This bit is always read as 1. The write value should

always be 1.

9 0 R Reserved

This bit is always read as 0. The write value should

always be 0.

8, 7 A2CL[1:0] 10 R/W CAS Latency for Area 2

Specify the CAS latency for area 2.

00: 1 cycle

01: 2 cycles

10: 3 cycles

11: 4 cycles

6 to 0 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

Note: * If only one area is connected to the SDRAM, specify area 3. In this case, specify area 2

as normal space or SRAM with byte selection.