Section 7 Interrupt Controller

Page 164 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

As shown in table 7.3, by setting the 4-bit groups (bits 15 to 12, bits 11 to 8, bits 7 to 4, and bits 3

to 0) with values from H'0 (0000) to H'F (1111), the priority of each corresponding interrupt is set.

Setting of H'0 means priority level 0 (the lowest level) and H'F means priority level 15 (the

highest level).

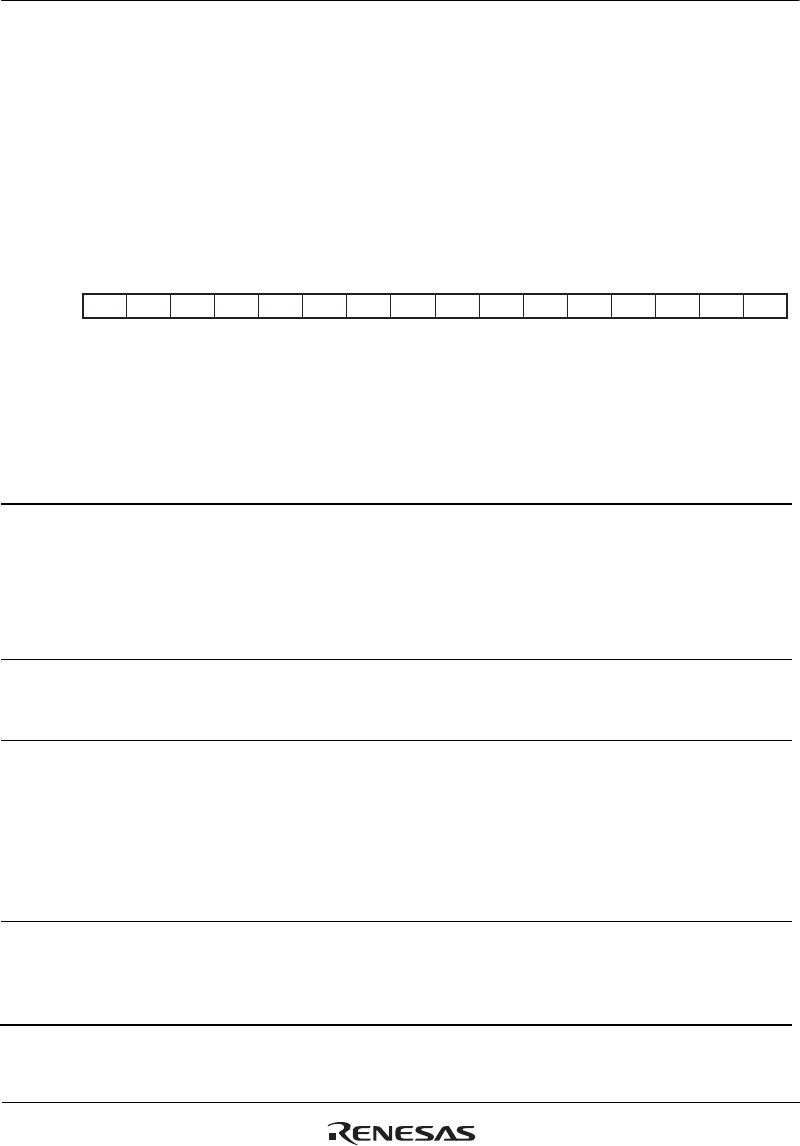

7.3.2 Interrupt Control Register 0 (ICR0)

ICR0 is a 16-bit register that sets the input signal detection mode for the external interrupt input

pin NMI, and indicates the input level at the NMI pin.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

*

1

000000000000001

RRRRRRRR/WRRRRRRR*

3

R/(W)*

2

*

3

Bit:

Initial value:

R/W:

Notes: 1 when the NMI pin is high, and 0 when the NMI pin is low.

Only 0 can be written to this bit.

Only 640-Kbyte version is valid.

1.

2.

3.

NMIL - - - - - - NMIE - - - - - - NMIF NMIM

Bit Bit Name

Initial

Value R/W Description

15 NMIL * R NMI Input Level

Sets the level of the signal input at the NMI pin. The

NMI pin level can be obtained by reading this bit. This

bit cannot be modified.

0: Low level is input to NMI pin

1: High level is input to NMI pin

14 to 9 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

8 NMIE 0 R/W NMI Edge Select

Selects whether the falling or rising edge of the

interrupt request signal on the NMI pin is detected.

0: Interrupt request is detected on falling edge of NMI

input

1: Interrupt request is detected on rising edge of NMI

input

7 to 2 All 0 R Reserved

Note: Only 640-Kbyte version is valid. For 1-Mbyte

version, these bits are reserved and always read

as 0. The write value should always be 0.