Section 13 Watchdog Timer

R01UH0134EJ0400 Rev. 4.00 Page 671 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

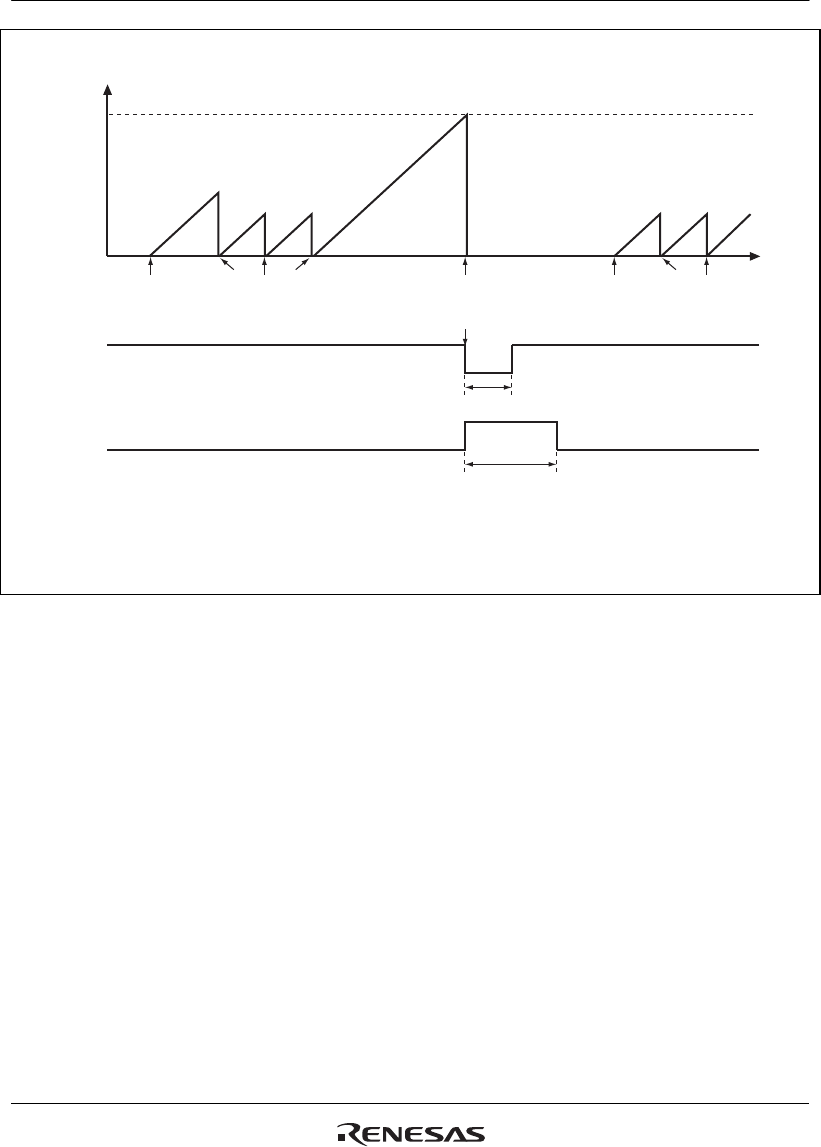

H'FF

H'00

Overflow

H'00 written

in WTCNT

Internal

reset signal*

WDTOVF

signal

WTCNT

value

WDTOVF and internal reset generated

WT/IT:

TME:

Timer mode select bit

Timer enable bit

H'00 written

in WTCNT

Time

128 × Pφ clock cycles

64 × Pφ clock cycles

Note: * Internal reset signal occurs only when the RSTE bit is set to 1.

[Legend]

WT/IT = 1

TME = 1

WOVF = 1

WT/IT = 1

TME = 1

Figure 13.4 Operation in Watchdog Timer Mode