Section 22 Renesas SPDIF Interface

R01UH0134EJ0400 Rev. 4.00 Page 1183 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

22.8.4 Transmitter Module Data Transfer

Once the transmitter module has left the idle state, it is ready for data transfer. Data transfer timing

can be achieved in three ways. Either the transfer is done by interrupts, DMA requests or by

polling the status register. There is a shared interrupt line (for both transmit and receive) and a

single transmitter DMA request line.

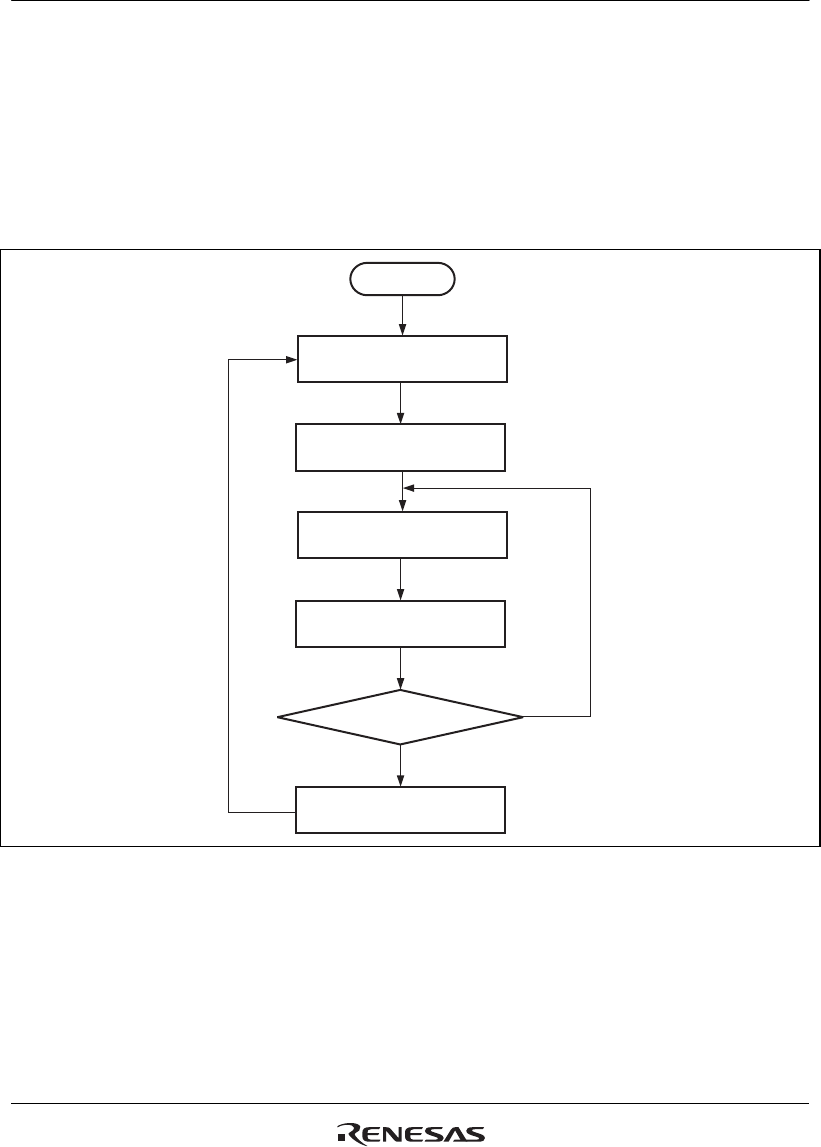

Figure 22.5 shows a data transfer with an interrupt for the transmitter.

Start

Idle

Wait for interrupt

Enter idle state?

No

Yes

Set control bit enabled

(TCBI)

Load left or right audio

channel data

Set control bit disabled

(TCBI)

Figure 22.5 Transmitter Data Transfer Flow Diagram - Interrupt Driven