Section 9 Bus State Controller

Page 278 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

(5) Burst ROM (Clocked Synchronous)

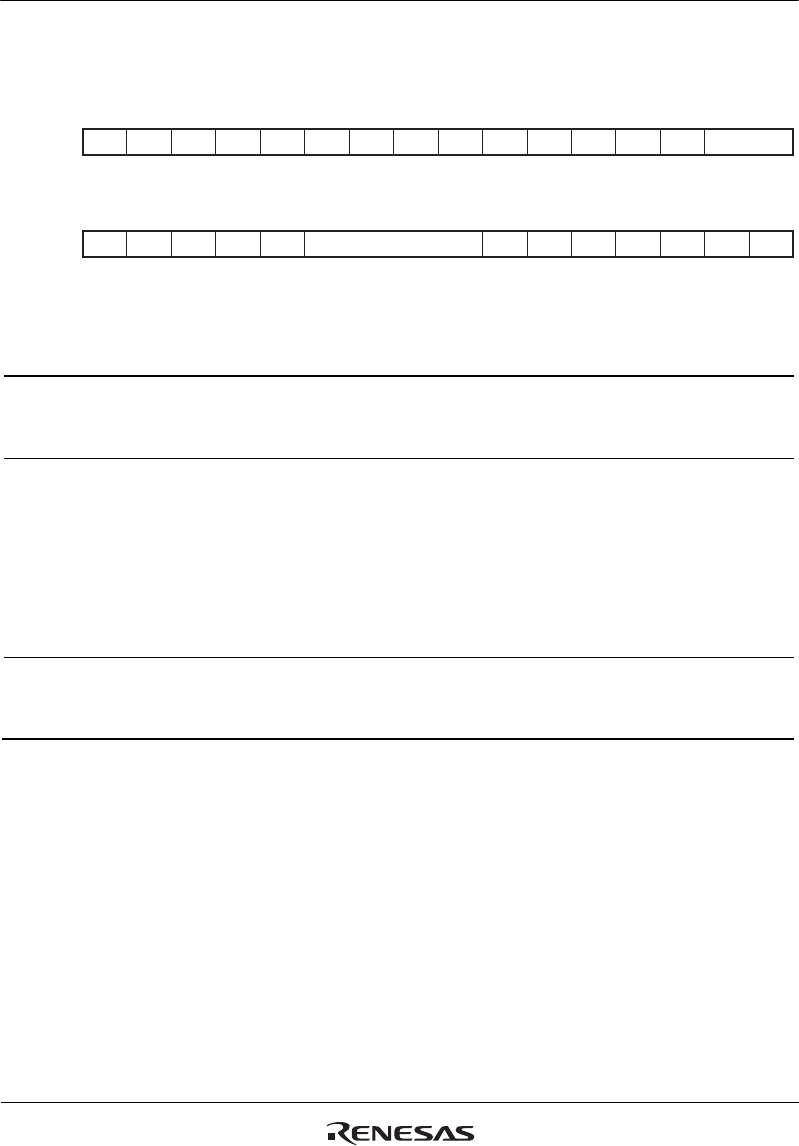

CS0WCR

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

RRRRRRRRRRRRRRR/WR/W

0000010100000000

R R R R R R/W R/W R/W R/W R/W R R R R R R

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

--------------BW[1:0]

- - - - - W[3:0] WM - - - - - -

Bit Bit Name

Initial

Value R/W Description

31 to 18 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

17, 16 BW[1:0] 00 R/W Number of Burst Wait Cycles

Specify the number of wait cycles to be inserted

between the second or subsequent access cycles in

burst access.

00: No cycle

01: 1 cycle

10: 2 cycles

11: 3 cycles

15 to 11 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.