Section 17 I

2

C Bus Interface 3

Page 856 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

17.3.2 I

2

C Bus Control Register 2 (ICCR2)

ICCR2 is an 8-bit readable/writable register that issues start/stop conditions, manipulates the SDA

pin, monitors the SCL pin, and controls reset in the control part of the I

2

C bus.

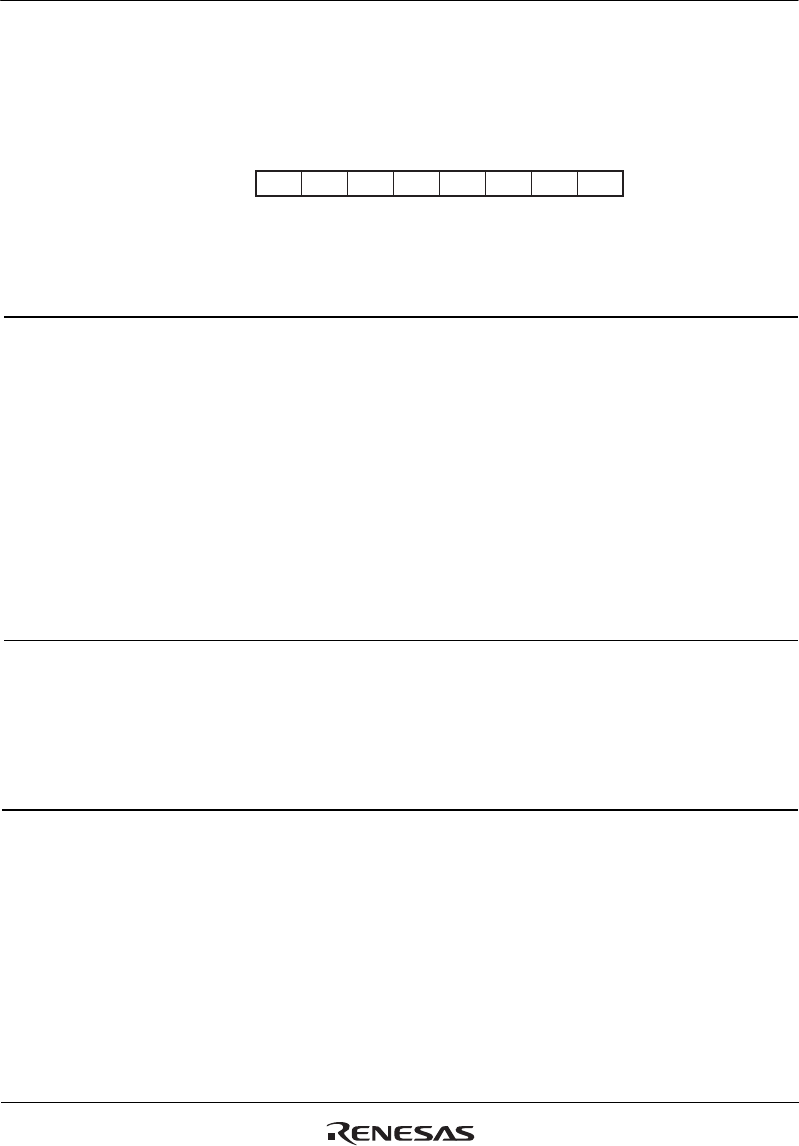

76543210

01111101

R/W R/W R/W R/W R R R/W R

Bit:

Initial value:

R/W:

BBSY SCP SDAO SDAOP SCLO

-

IICRST

-

Bit Bit Name

Initial

Value R/W Description

7 BBSY 0 R/W Bus Busy

Enables to confirm whether the I

2

C bus is occupied or

released and to issue start/stop conditions in master

mode. With the clocked synchronous serial format, this

bit is always read as 0. With the I

2

C bus format, this bit

is set to 1 when the SDA level changes from high to low

under the condition of SCL = high, assuming that the

start condition has been issued. This bit is cleared to 0

when the SDA level changes from low to high under the

condition of SCL = high, assuming that the stop

condition has been issued. Write 1 to BBSY and 0 to

SCP to issue a start condition. Follow this procedure

when also re-transmitting a start condition. Write 0 in

BBSY and 0 in SCP to issue a stop condition.

6 SCP 1 R/W Start/Stop Issue Condition Disable

Controls the issue of start/stop conditions in master

mode. To issue a start condition, write 1 in BBSY and 0

in SCP. A retransmit start condition is issued in the

same way. To issue a stop condition, write 0 in BBSY

and 0 in SCP. This bit is always read as 1. Even if 1 is

written to this bit, the data will not be stored.