Section 20 Controller Area Network

R01UH0134EJ0400 Rev. 4.00 Page 1027 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

(1) Transmit Pending Register (TXPR1, TXPR0)

The concatenation of TXPR1 and TXPR0 is a 32-bit register that contains any transmit pending

flags for the CAN module. In the case of 16-bit bus interface, Long Word access is carried out as

two consecutive word accesses.

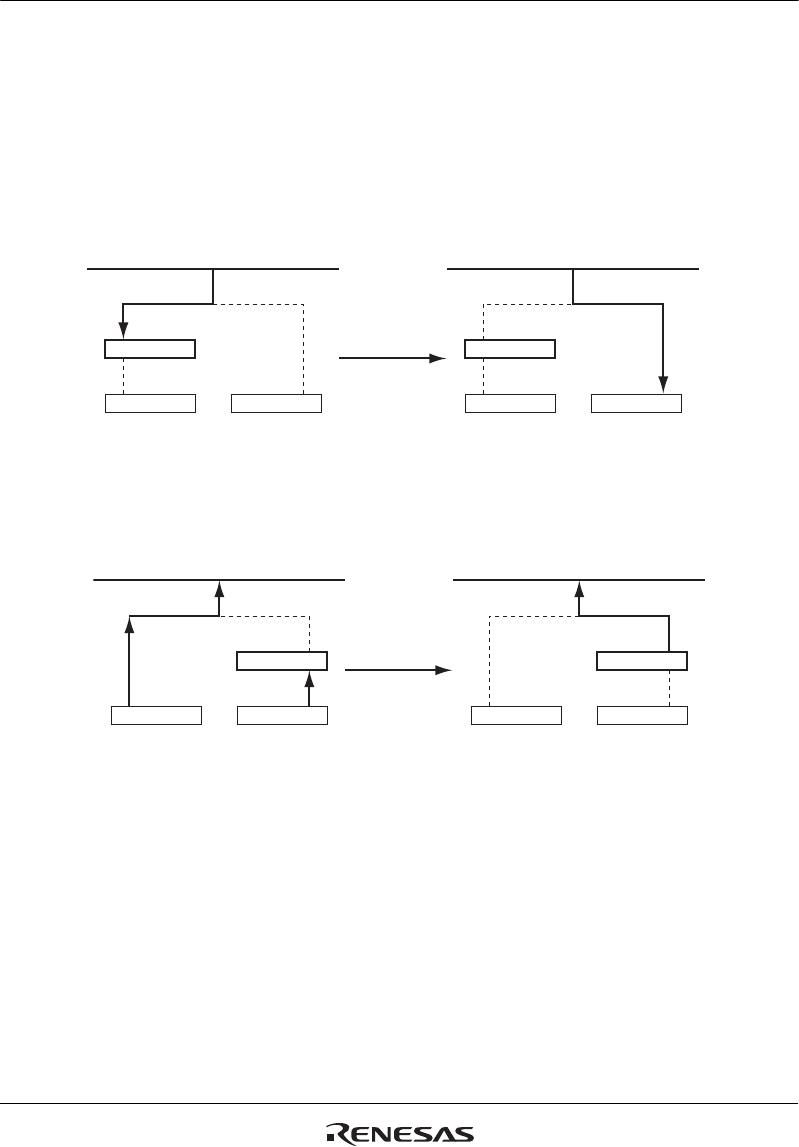

<Longword Write Operation>

Temp

TXPR1 TXPR0

H'020 H'022

<upper word write>

16-bit Peripheral bus

Data is stored into Temp instead of TXPR1.

consecutive access

<lower word write>

16-bit Peripheral bus

Longword data are stored into

both TXPR1 and TXPR0 at the same time.

Temp

TXPR1 TXPR0

H'020

H'022

<Longword Read Operation>

Temp

TXPR1 TXPR0

H'020 H'022

<upper word read>

16-bit Peripheral bus

TXPR0 is stored into Temp,

when TXPR1 is read.

consecutive access

<lower word read>

16-bit Peripheral bus

Temp is read instead of TXPR0.

Temp

TXPR1 TXPR0

H'020

H'022

The TXPR1 controls Mailbox-31 to Mailbox-16, and the TXPR0 controls Mailbox-15 to Mailbox-

1. The CPU may set the TXPR bits to affect any message being considered for transmission by

writing a '1' to the corresponding bit location. Writing a '0' has no effect, and TXPR cannot be

cleared by writing a '0' and must be cleared by setting the corresponding TXCR bits. TXPR may

be read by the CPU to determine which, if any, transmissions are pending or in progress. In effect

there is a transmit pending bit for all Mailboxes except for the Mailbox-0. Writing a '1' to a bit

location when the mailbox is not configured to transmit is not allowed.