Section 9 Bus State Controller

Page 360 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

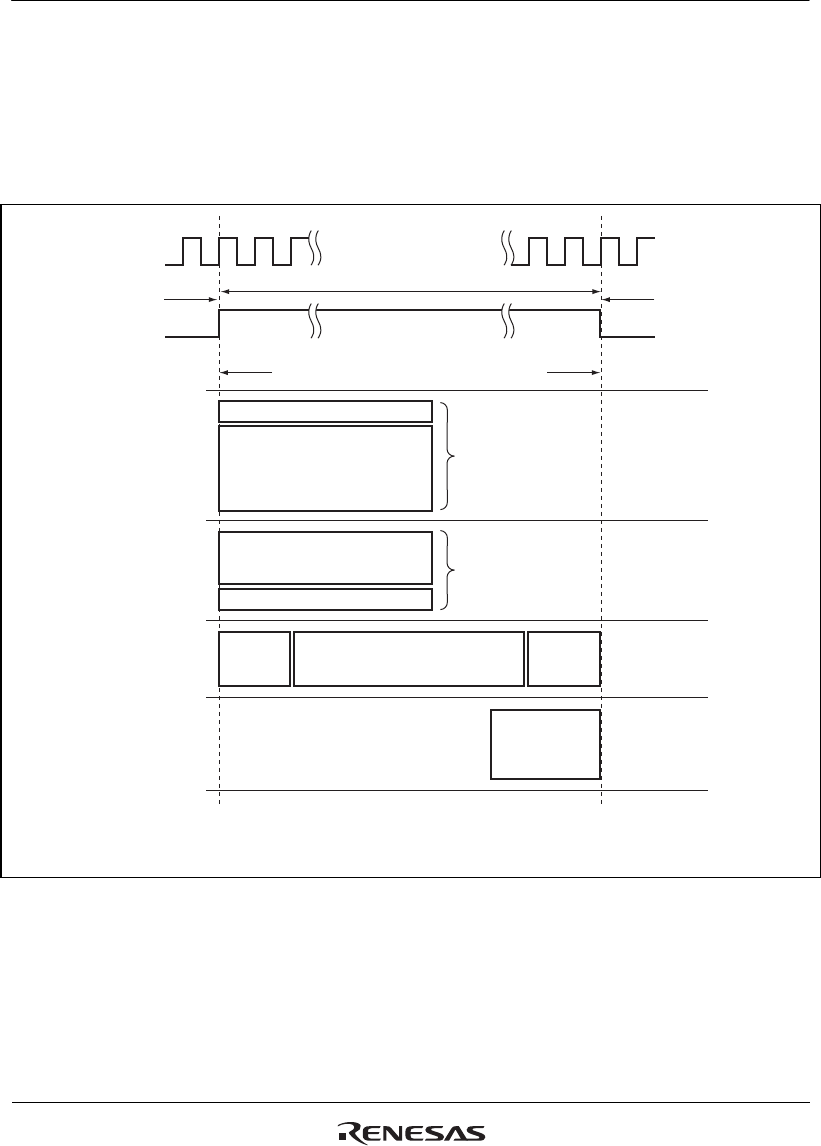

In the above conditions, a total of four conditions, that is, condition [1] or [2] (either one is

effective), condition [3] or [4] (either one is effective), a set of conditions [5] to [7] (these are

generated successively, and therefore the sum of them should be taken as one set of idle cycles),

and condition [8] are generated at the same time. The maximum number of idle cycles among

these four conditions become the number of idle cycles on the external bus. To ensure the

minimum idle cycles, be sure to make register settings for condition [1] or [2].

CKIO

CSn

Previous access

External bus idle cycles

Idle cycle after access

Either one of them

is effective

[1]

DMAIW[2:0] setting in CMNCR

[2]

IWW[2:0] setting in CSnBCR

IWRWD[2:0] setting in CSnBCR

IWRWS[2:0] setting in CSnBCR

IWRRD[2:0] setting in CSnBCR

IWRRS[2:0] setting in CSnBCR

[3]

WTRP[1:0] setting in CSnWCR

TRWL[1:0] setting in CSnWCR

WTRC[1:0] setting in CSnWCR

[4]

WM setting in CSnWCR

[6]

Internal bus idle cycles, etc.

[8]

Idle cycles

between

different

memory types

[5]

Read

data

transfer

[7]

Write

data

wait

Idle cycle before access

Next access

Condition [1] or [2]

A total of four conditions (condition [1] or [2], condition [3] or [4], a set of conditions [5] to [7],

and condition [8]) generate idle cycle at the same time. Accordingly, the maximum number of

cycles among these four conditions become the number of idle cycles.

Note:

Condition [8]

Condition [3] or [4]

Set of conditions

[5] to [7]

Either one of them

is effective

Figure 9.45 Idle Cycle Conditions