Section 15 Serial Communication Interface with FIFO

Page 720 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

15.3.6 Serial Control Register (SCSCR)

SCSCR enables/disables the transmitter/receiver operation and interrupt requests, and selects the

transmit/receive clock source. The CPU can always read and write to SCSCR.

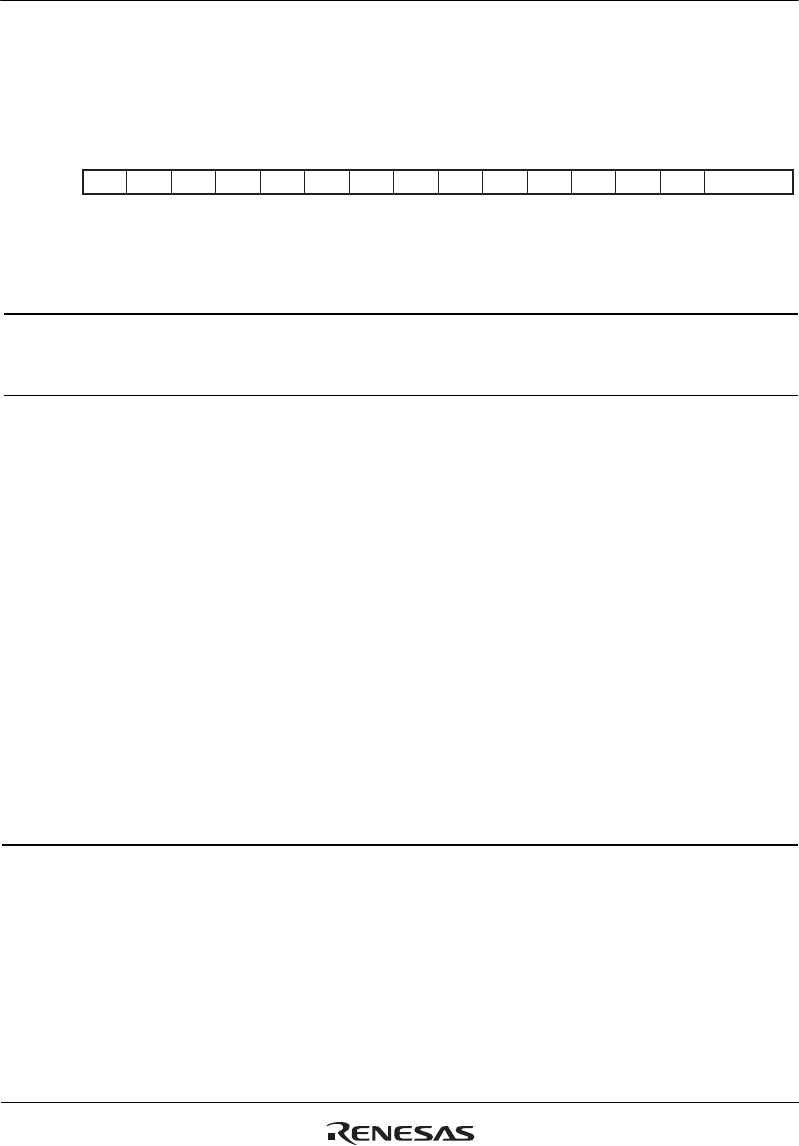

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

R R R R R R R R R/W R/W R/W R/W R/W R R/W R/W

Bit:

Initial value:

R/W:

- - - - - - - - TIE RIE TE RE REIE - CKE[1:0]

Bit Bit Name

Initial

Value R/W Description

15 to 8 All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

7 TIE 0 R/W Transmit Interrupt Enable

Enables or disables the transmit-FIFO-data-empty

interrupt (TXI) requested when the serial transmit data

is transferred from the transmit FIFO data register

(SCFTDR) to the transmit shift register (SCTSR), when

the quantity of data in the transmit FIFO register

becomes less than the specified number of

transmission triggers, and when the TDFE flag in the

serial status register (SCFSR) is set to1.

0: Transmit-FIFO-data-empty interrupt request (TXI) is

disabled

1: Transmit-FIFO-data-empty interrupt request (TXI) is

enabled*

Note: * The TXI interrupt request can be cleared by

writing a greater quantity of transmit data

than the specified transmission trigger

number to SCFTDR and by clearing TDFE

to 0 after reading 1 from TDFE, or can be

cleared by clearing TIE to 0.