Section 7 Interrupt Controller

Page 198 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

F

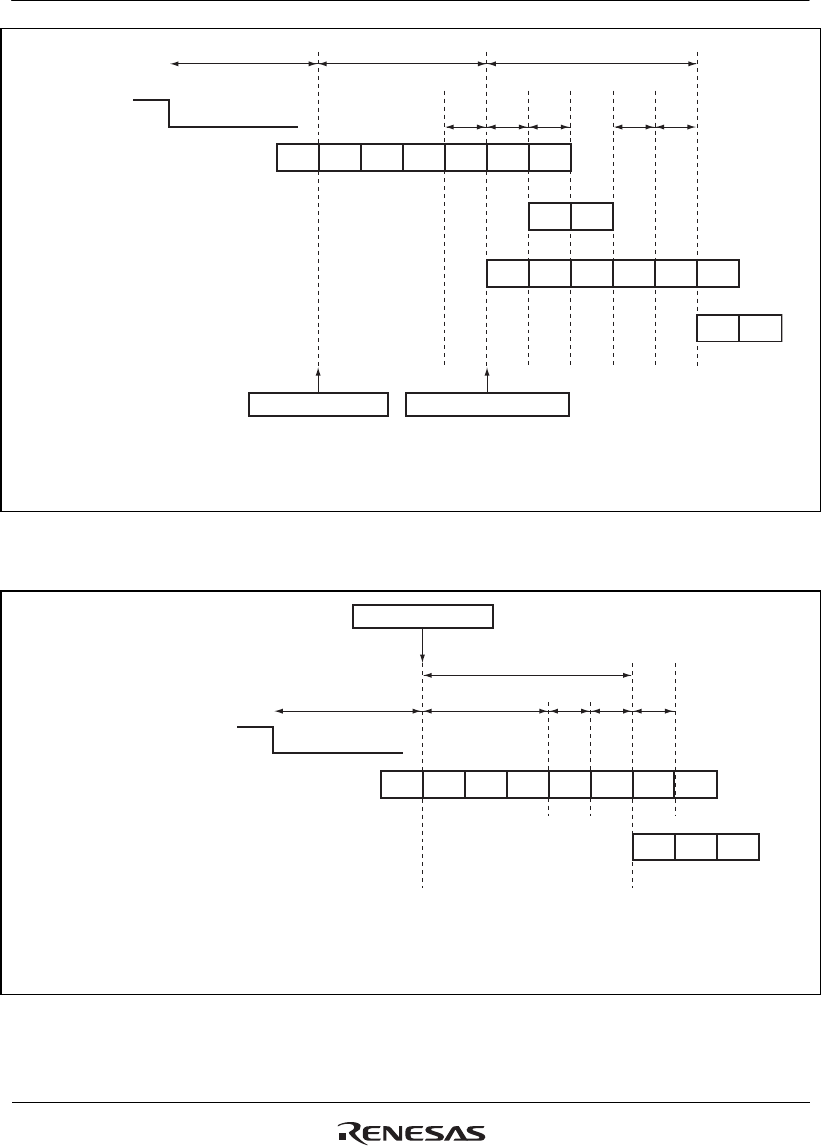

2 Icyc + 3 Bcyc + 1 Pcyc 1 Icyc + m1 + 2(m2) + m3

m1 m2 m3

3 Icyc + m1

IRQ

DEEMMM

DEEMM

M

F

D

F D

m1

m2

[Legend]

m1:

m2:

m3:

Vector address read

Saving of SR (stack)

Saving of PC (stack)

Interrupt acceptance

Multiple interrupt acceptance

First instruction in interrupt exception

service routine

First instruction in multiple interrupt

exception service routine

Figure 7.5 Example of Pipeline Operation for Multiple Interrupts

(No Register Banking)

F

2 Icyc + 3 Bcyc + 1 Pcyc 3 Icyc m1 m2 m3

3 Icyc + m1 + m2

IRQ

DEEMMM

E

FD

E

[Legend]

m1:

m2:

m3:

Vector address read

Saving of SR (stack)

Saving of PC (stack)

Interrupt acceptance

First instruction in interrupt exception

service routine

Instruction (instruction replacing

interrupt exception handling)

Figure 7.6 Example of Pipeline Operation when IRQ Interrupt is Accepted

(Register Banking without Register Bank Overflow)