Section 37 Electrical Characteristics

R01UH0134EJ0400 Rev. 4.00 Page 2039 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

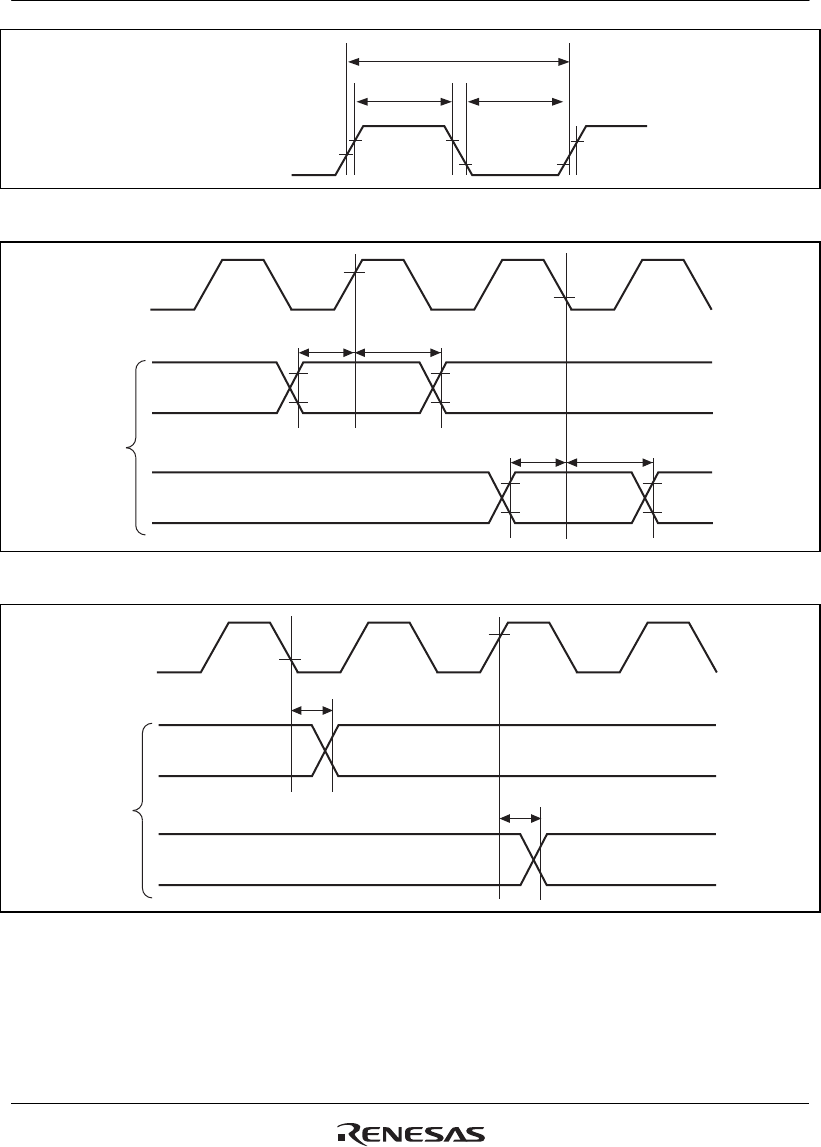

t

cyc

t

WIL

t

WIH

V

OH

1/2 PVcc

LCD_CLK

V

OH

V

OL

V

OL

Figure 37.72 LCD_CLK Clock Output Timing

DV_CLK

Latched at

rising edge

Latched at

falling edge

t

VS

t

VH

t

VS

t

VH

DV_DATA7 to

DV_DATA0,

DV_VSYNC,

DV_HSYNC

Figure 37.73 Video Input Timing

LCD_CLK

Output at

falling edge

Output at

rising edge

t

DD

t

DD

LCD_DATA15 to

LCD_DATA0,

LCD_VSYNC,

LCD_HSYNC,

LCD_DE,

LCD_M_DISP

Figure 37.74 Display Output Timing