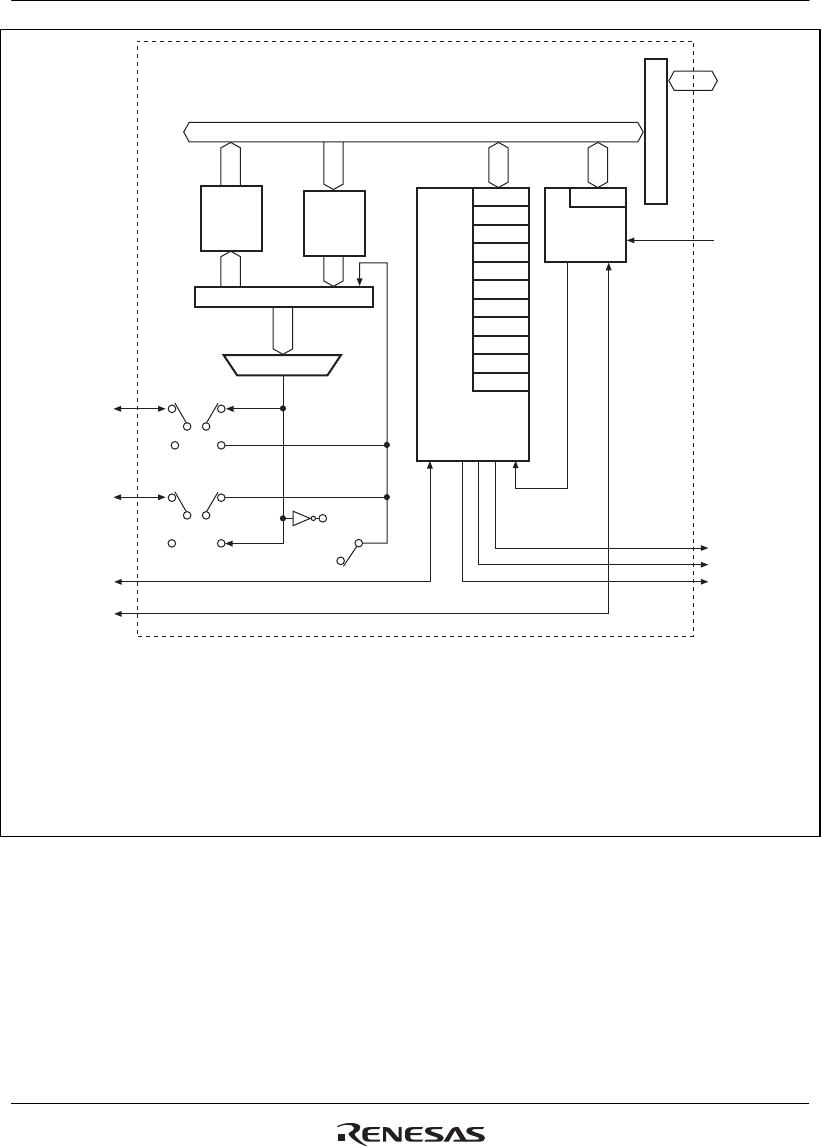

Section 16 Renesas Serial Peripheral Interface

R01UH0134EJ0400 Rev. 4.00 Page 777 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Bus interface

Module data bus

Transmission/

reception

controller

Clock

Baud rate

generator

SPCR

SSLP

SPPCR

SPSR

SPDCR

SPCKD

SSLND

SPND

SPCMD

SPBFCR

SPBFDR

MOSI

MISO

Shift register

Selector

Master

Slave

Normal

MasterNormal

Normal

Peripheral bus

SPTI

SPRI

SPEI

SSL

RSPCK

Bφ

Loopback

SlaveLoopback

Loopback

SPBR

SPRX

(FIFO

structure)

32 bytes

SPTX

(FIFO

structure)

8 bytes

[Legend]

SPCR:

SSLP:

SPPCR:

SPSR:

SPSCR:

SPSSR:

SPDCR:

SPCKD:

SSLND:

SPND:

Control register

Slave select polarity register

Pin control register

Satus register

Sequence control register

Sequence status register

Data control register

Cock delay register

Slave select negate delay register

Next-access delay register

SPCMD:

SPBR:

SPTX:

SPRX:

SPBFCR:

SPBFDR:

SPTI:

SPRI:

SPEI:

Command register

Bit rate register

Transmission buffer

(Data register write side)

Receive buffer

(Data register read side)

Buffer control register

Buffer data count setting register

Transmit interrupt

Receive interrupt

Error interrupt

Figure 16.1 Block Diagram (for One Channel)