Section 26 USB 2.0 Host/Function Module

Page 1518 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

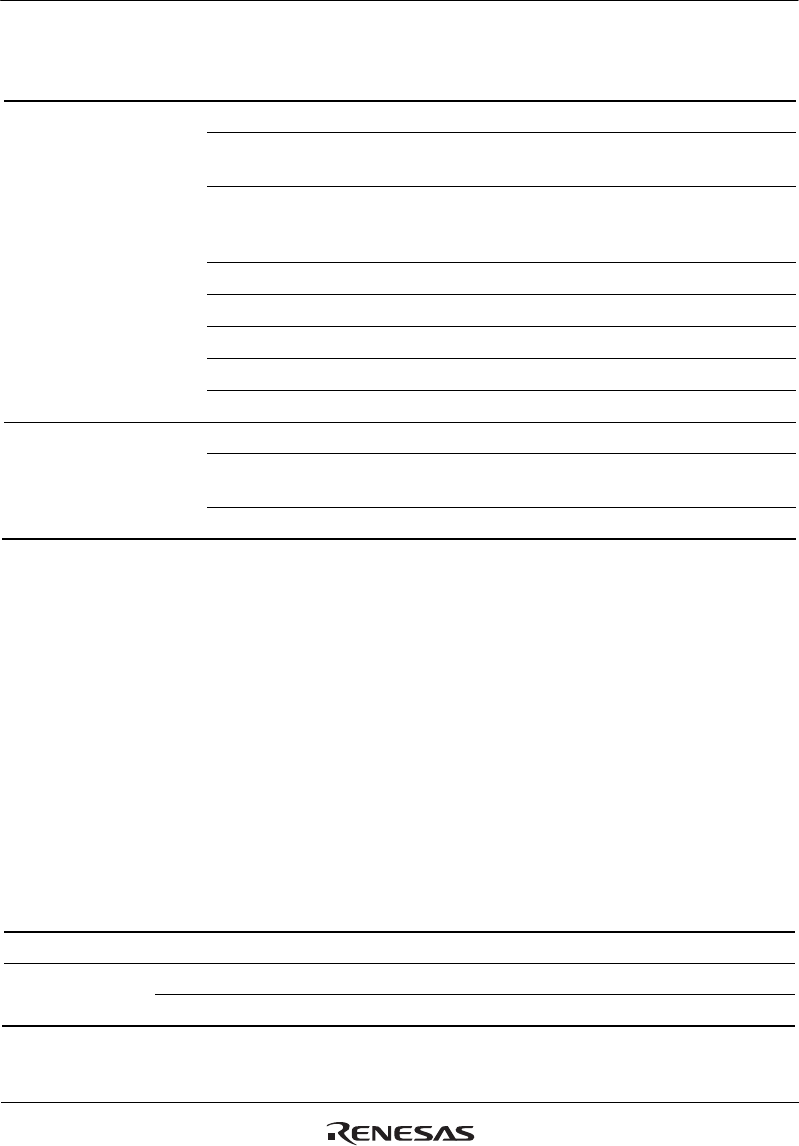

Table 26.23 FIFO Port Function Settings

Register Name Bit Name Function Note

C/DnFIFOSEL RCNT Selects DTLN read mode

REW Buffer memory rewind (re-read,

rewrite)

DCLRM Automatically clears data received for

a specified pipe after the data has

been read

For DnFIFO only

DREQE Enables DMA transfers For DnFIFO only

MBW FIFO port access bit width

BIGEND Selects FIFO port endian

ISEL FIFO port access direction

CURPIPE Selects the current pipe For DCP only

C/DnFIFOCTR BVAL Ends writing to the buffer memory

BCLR Clears the buffer memory on the CPU

side

DTLN Checks the length of received data

(a) FIFO Port Selection

Table 26.24 shows the pipes that can be selected with the various FIFO ports. The pipe to be

accessed is selected using the CURPIPE bit in C/DnFIFOSEL. After the pipe is selected, whether

the CURPIPE value for the pipe, which was written last, can be correctly read should be checked.

(If the previous pipe number is read, it indicates that the pipe modification is being executed by

this module.) Then, the FIFO port can be accessed after FRDY = 1 is checked .

Also, the bus width to be accessed should be selected using the MBW bit. The buffer memory

access direction conforms to the DIR bit in PIPECFG. The ISEL bit determines this only for the

DCP.

Table 26.24 FIFO Port Access Categorized by Pipe

Pipe Access Method Port that can be Used

DCP CPU access CFIFO port register

PIPE1 to PIPE9 CPU access CFIFO port register

DMA access D0FIFO/D1FIFO port register