Section 9 Bus State Controller

Page 284 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

9.4.5 Refresh Timer Control/Status Register (RTCSR)

RTCSR specifies various items about refresh for SDRAM.

When RTCSR is written, the upper 16 bits of the write data must be H'A55A to cancel write

protection.

The phase of the clock for incrementing the count in the refresh timer counter (RTCNT) is

adjusted only by a power-on reset. Note that there is an error in the time until the compare match

flag is set for the first time after the timer is started with the CKS[2:0] bits being set to a value

other than B'000.

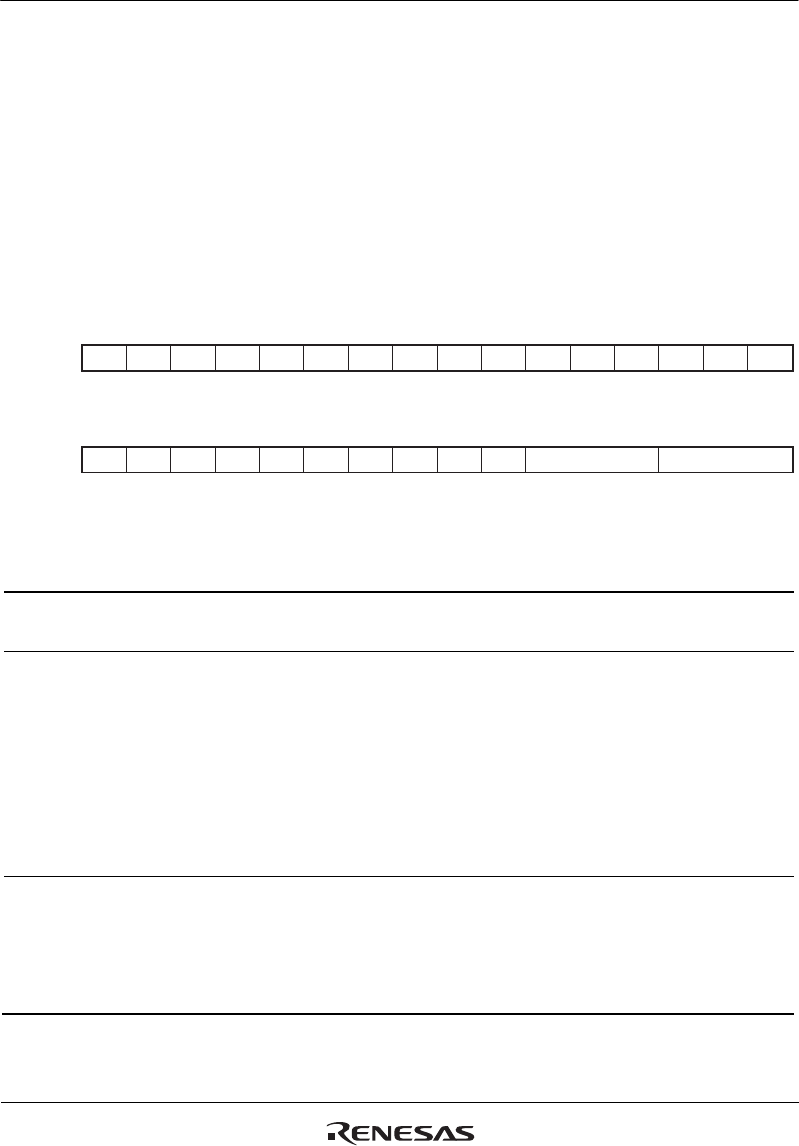

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

RRRRRRRRRRRRRRRR

0000000000000000

R R R R R R R R R/W R/W R/W R/W R/W R/W R/W R/W

Bit:

Initial value:

R/W:

Bit:

Initial value:

R/W:

----------------

- - - - - - - - CMF CMIE CKS[2:0] RRC[2:0]

Bit Bit Name

Initial

Value R/W Description

31 to 8 All 0 R Reserved

These bits are always read as 0.

7 CMF 0 R/W Compare Match Flag

Indicates that a compare match occurs between the

refresh timer counter (RTCNT) and refresh time

constant register (RTCOR). This bit is set or cleared

in the following conditions.

0: Clearing condition: When 0 is written in CMF after

reading out RTCSR during CMF = 1.

1: Setting condition: When the condition RTCNT =

RTCOR is satisfied.

6 CMIE 0 R/W Compare Match Interrupt Enable

Enables or disables CMF interrupt requests when the

CMF bit in RTCSR is set to 1.

0: Disables CMF interrupt requests.

1: Enables CMF interrupt requests.