Section 10 Direct Memory Access Controller

Page 422 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

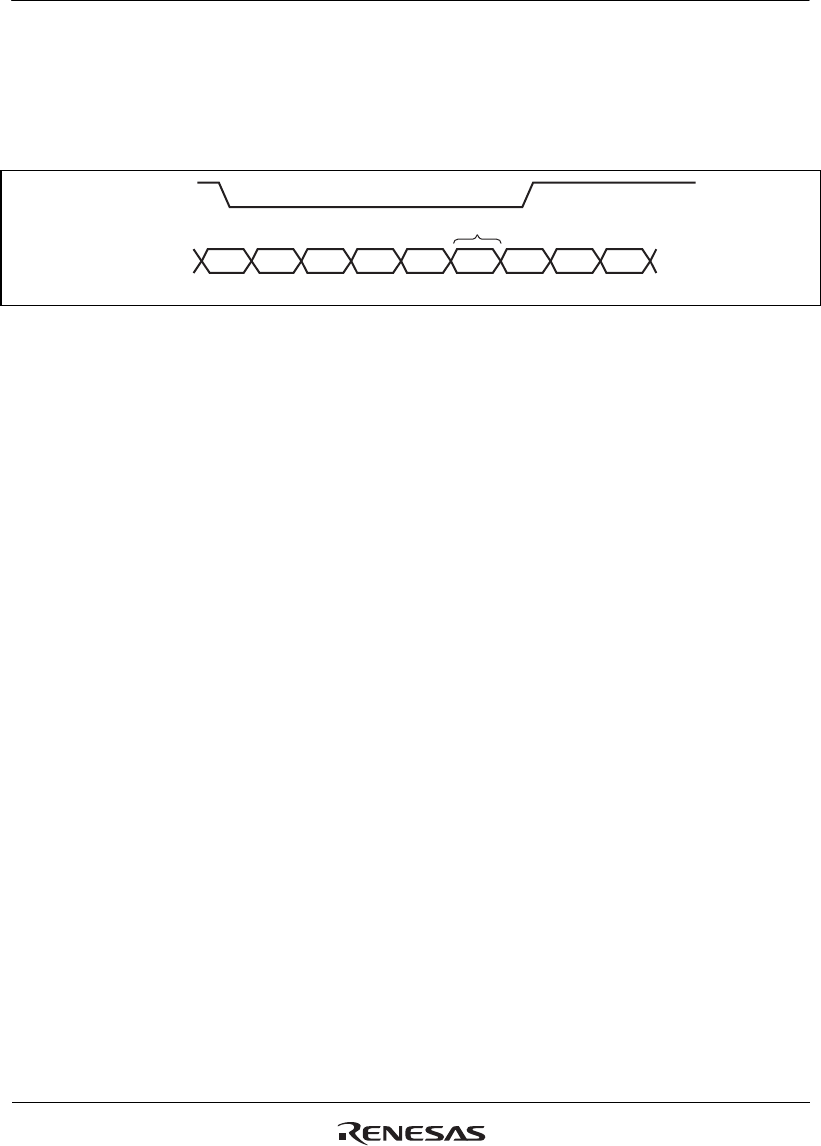

Figure 10.7 shows an example of DMA transfer timing in cycle-steal normal mode. Transfer

conditions shown in the figure are;

Dual address mode

DREQ low level detection

CPU CPU CPU DMA DMA CPU DMA DMA CPU

DREQ

Bus cycle

Bus mastership returned to CPU once

Read/Write Read/Write

Figure 10.7 DMA Transfer Example in Cycle-Steal Normal Mode

(Dual Address, DREQ Low Level Detection)

Intermittent Mode 16 and Intermittent Mode 64

In intermittent mode of cycle steal, this module returns the bus mastership to other bus master

whenever a unit of transfer (byte, word, longword, or 16 bytes) is completed. If the next

transfer request occurs after that, this module obtains the bus mastership from other bus master

after waiting for 16 or 64 cycles of B clock. This module then transfers data of one unit and

returns the bus mastership to other bus master. These operations are repeated until the transfer

end condition is satisfied. It is thus possible to make lower the ratio of bus occupation by

DMA transfer than the normal mode of cycle steal.

When this module obtains again the bus mastership, DMA transfer may be postponed in case

of entry updating due to cache miss.

The cycle-steal intermittent mode can be used for any transfer section; transfer request source,

transfer source, and transfer destination. The bus modes, however, must be cycle steal mode in

all channels.

Figure 10.8 shows an example of DMA transfer timing in cycle-steal intermittent mode.

Transfer conditions shown in the figure are;

Dual address mode

DREQ low level detection