Section 33 Power-Down Modes

Page 1796 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

33.2.15 On-Chip Data-Retention RAM Area Setting Register (RRAMKP)

RRAMKP is an 8-bit readable/writable register that selects whether the contents of the

corresponding area of the on-chip data-retention RAM are retained or not in deep standby mode.

When the RRAMKP3 to RRAMKP0 bits are set to 1, the contents of the corresponding area of the

on-chip data-retention RAM are retained in deep standby mode. When these bits are cleared to 0,

the contents of the corresponding area of the on-chip data-retention RAM are not retained in deep

standby mode.

Note: When writing to this register, see section 33.4, Usage Notes.

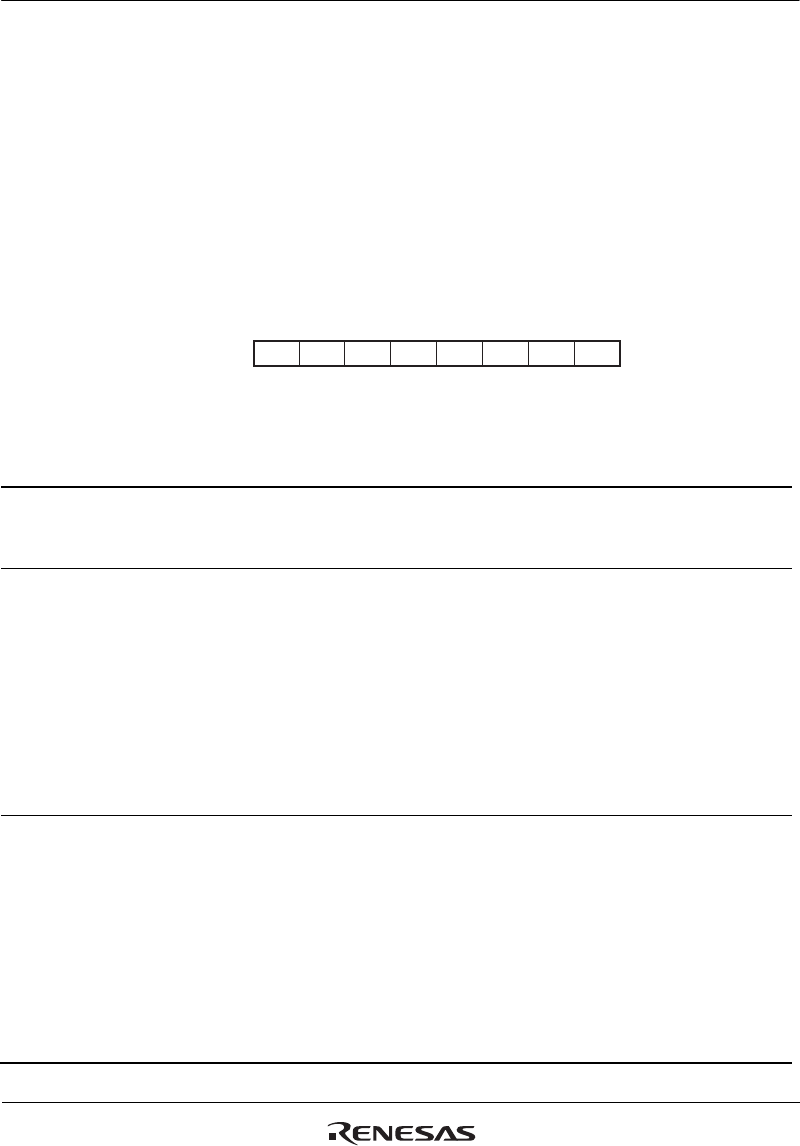

76543210

Bit:

Initial value:

R/W:

00000000

R R R R R/W R/W R/W R/W

----

RRAM

KP3

RRAM

KP2

RRAM

KP0

RRAM

KP1

Bit Bit Name

Initial

Value R/W Description

7 to 4 All 0 R Reserved

These bits are always read as 0. The write value

should always be 0.

3 RRAMKP3 0 R/W On-Chip Data-Retention RAM Storage Area 3

(corresponding area: page 3* in on-chip data-

retention RAM)

0: The contents of the on-chip data-retention RAM

are not retained in deep standby mode.

1: The contents of the on-chip data-retention RAM

are retained in deep standby mode.

Note: For 1-Mbyte version, this bit is reserved and

always read as 0. The write value should

always be 0.

2 RRAMKP2 0 R/W On-Chip Data-Retention RAM Storage Area 2

(corresponding area: page 2* in on-chip data-

retention RAM)

0: The contents of the on-chip data-retention RAM

are not retained in deep standby mode.

1: The contents of the on-chip data-retention RAM

are retained in deep standby mode.

Note: For 1-Mbyte version, this bit is reserved and

always read as 0. The write value should

always be 0.