Section 22 Renesas SPDIF Interface

R01UH0134EJ0400 Rev. 4.00 Page 1155 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

22.6 Register

Table 22.3 shows the register configuration.

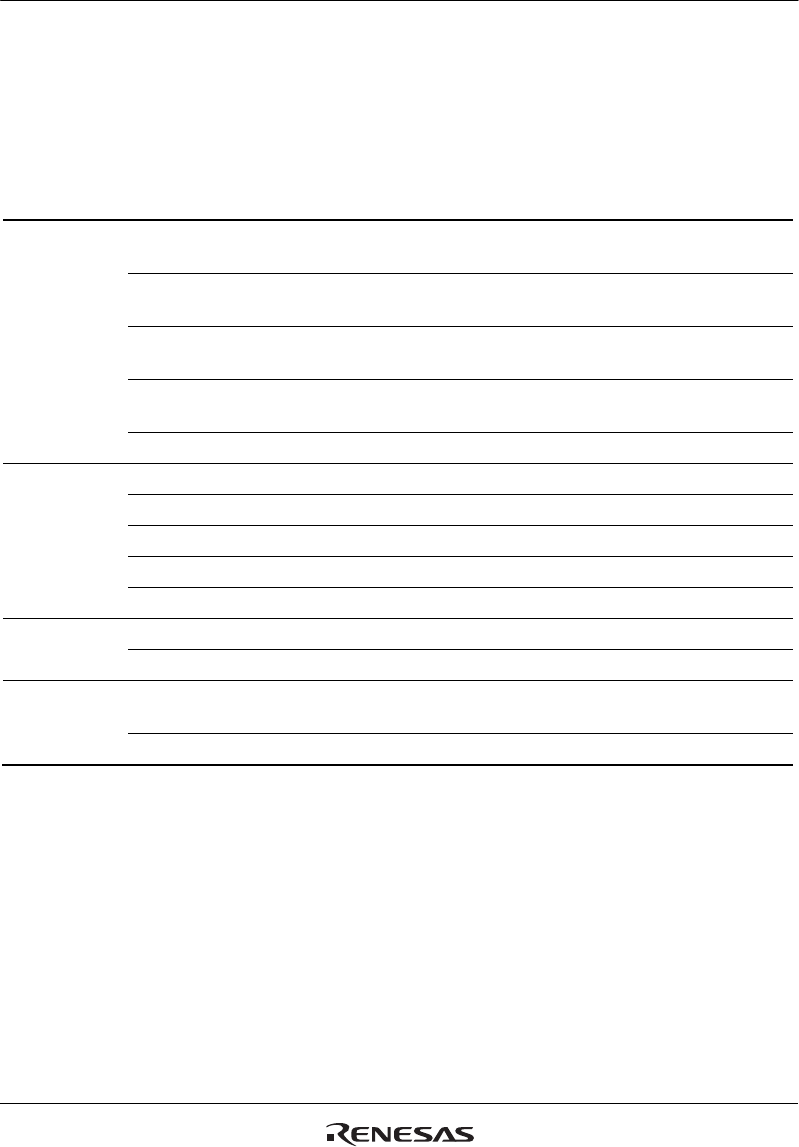

Table 22.3 Register Configuration

Channel Register Name Abbreviation Address

Access

Size

0

(Transmit)

Transmitter channel 1 audio

register

TLCA H'FFFF 5800 32

Transmitter channel 2 audio

register

TRCA H'FFFF 5804 32

Transmitter channel 1 status

register

TLCS H'FFFF 5808 32

Transmitter channel 2 status

register

TRCS H'FFFF 580C 32

Transmitter user data register TUI H'FFFF 5810 32

1

(Receive)

Receiver channel 1 audio register RLCA H'FFFF 5814 32

Receiver channel 2 audio register RRCA H'FFFF 5818 32

Receiver channel 1 status register RLCS H'FFFF 581C 32

Receiver channel 2 status register RRCS H'FFFF 5820 32

Receiver user data register RUI H'FFFF 5824 32

0, 1

(Common)

Control register CTRL H'FFFF 5828 32

Status register STAT H'FFFF 582C 32

0, 1

(Common)

Transmitter DMA audio data

register

TDAD H'FFFF 5830 32

Receiver DMA audio data register RDAD H'FFFF 5834 32

Note: All registers are longword registers and must be accessed as such.

A register diagram containing a 0 indicates that the write value should always be 0 (if the

register is writeable) and that the read value should always be 0 (if readable).