Section 27 Video Display Controller 3

R01UH0134EJ0400 Rev. 4.00 Page 1567 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

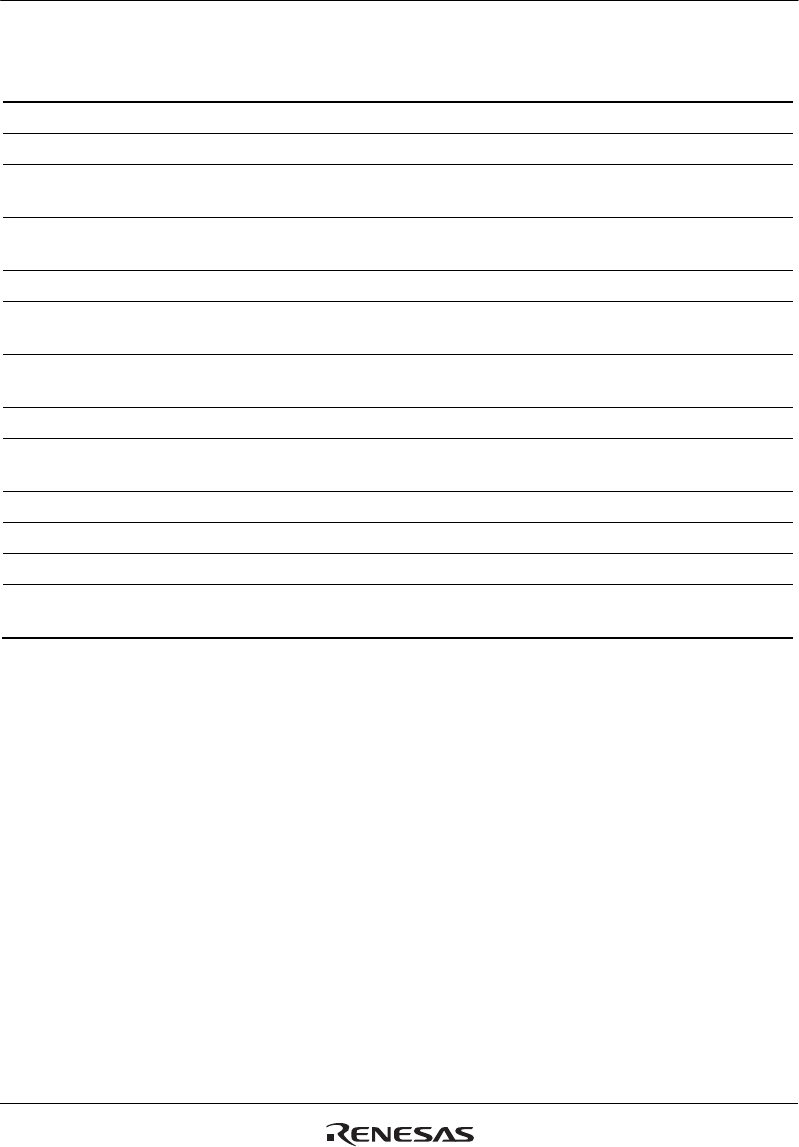

Table 27.8 Register Configuration in Graphics Block 1

Register Name Abbreviation R/W Initial Value Address Access Size

Graphics block control register GRCMEN1 R/W H'0000 0000 H'FFFF 2800 32, 16, 8

Bus control register GRCBUSCNT1 R/W H'0000 0000 H'FFFF 2804 32, 16, 8

Graphics block interrupt control

register

GRCINTCNT1 R/W H'0000 0000 H'FFFF 2808 32, 16, 8

Graphics image base address

register

GROPSADR1 R/W H'0000 0000 H'FFFF 2B08 32, 16, 8

Graphics image size register GROPSWH1 R/W H'0000 0000 H'FFFF 2B0C 32, 16, 8

Graphics image line offset

register

GROPSOFST1 R/W H'0000 0000 H'FFFF 2B10 32, 16, 8

Graphics image start position

register

GROPDPHV1 R/W H'0000 0000 H'FFFF 2B14 32, 16, 8

control area size register GROPEWH1 R/W H'0000 0000 H'FFFF 2B18 32, 16, 8

control area start position

register

GROPEDPHV1 R/W H'0000 0000 H'FFFF 2B1C 32, 16, 8

control register GROPEDPA1 R/W H'FF00 0000 H'FFFF 2B20 32, 16, 8

Chroma-key control register GROPCRKY0_1 R/W H'0000 0000 H'FFFF 2B24 32, 16, 8

Chroma-key color register GROPCRKY1_1 R/W H'0000 0000 H'FFFF 2B28 32, 16, 8

Color register for outside of

graphics image area

GROPBASERGB1 R/W H'0000 0000 H'FFFF 2B2C 32, 16, 8