Section 37 Electrical Characteristics

R01UH0134EJ0400 Rev. 4.00 Page 2007 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Notes: 1. An address pin to be connected to pin A10 of SDRAM.

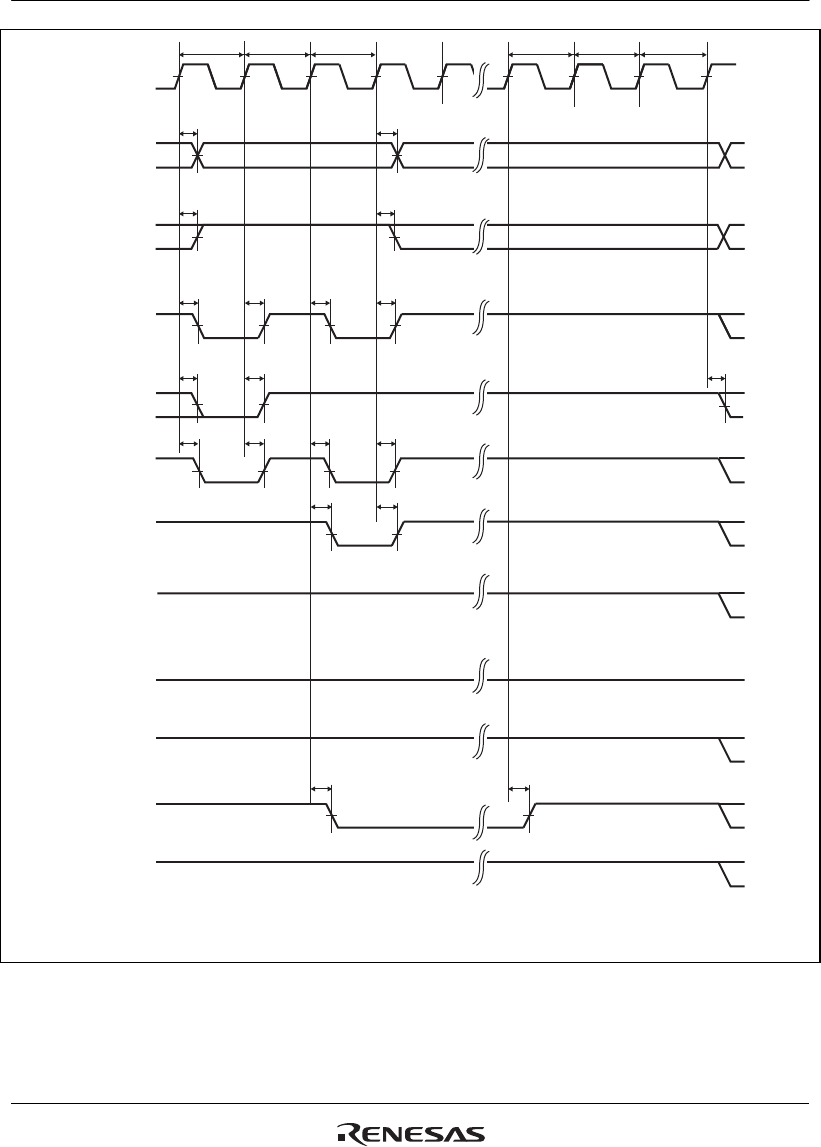

2. The waveform for DACKn and TENDn is when active low is specified.

Tr c Tr c TrcTr rTpwTp

t

CSD1

t

AD1

t

AD1

t

RWD1

t

RWD1

t

RWD1

t

CSD1

t

CSD1

t

CSD1

t

RASD1

t

RASD1

t

RASD1

t

RASD1

t

AD1

t

AD1

CKIO

A25 to A0

CSn

RD/WR

A12/A11

*

1

D15 to D0

RAS

t

CASD1

t

CASD1

CAS

(Hi-Z)

BS

CKE

DQMxx

DACKn

TENDn

*

2

t

CKED1

t

CKED1

Figure 37.32 Synchronous DRAM Self-Refreshing Timing

(WTRP = 1 Cycle)