Section 11 Multi-Function Timer Pulse Unit 2

Page 466 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

11.3.4 Timer Interrupt Enable Register (TIER)

The TIER registers are 8-bit readable/writable registers that control enabling or disabling of

interrupt requests for each channel. This module has six TIER registers, two for channel 0 and one

each for channels 1 to 4.

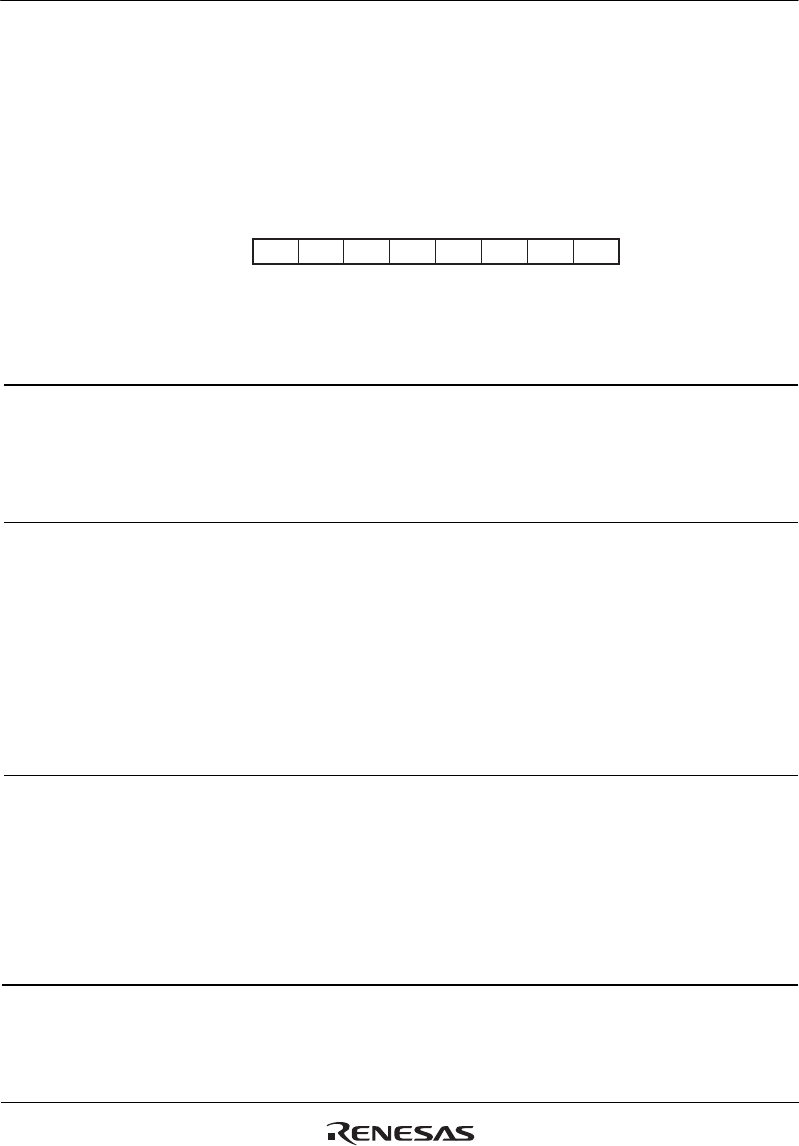

TIER_0, TIER_1, TIER_2, TIER_3, TIER_4

76543210

Bit:

Initial value:

R/W:

00000000

R/W R/W R/W R/W R/W R/W R/W R/W

TTGE TTGE2 TCIEU TCIEV TGIED TGIEC TGIEB TGIEA

Bit Bit Name

Initial

Value R/W Description

7 TTGE 0 R/W A/D Converter Start Request Enable

Enables or disables generation of A/D converter start

requests by TGRA input capture/compare match.

0: A/D converter start request generation disabled

1: A/D converter start request generation enabled

6 TTGE2 0 R/W A/D Converter Start Request Enable 2

Enables or disables generation of A/D converter start

requests by TCNT_4 underflow (trough) in

complementary PWM mode.

In channels 0 to 3, bit 6 is reserved. It is always read as

0 and the write value should always be 0.

0: A/D converter start request generation by TCNT_4

underflow (trough) disabled

1: A/D converter start request generation by TCNT_4

underflow (trough) enabled

5 TCIEU 0 R/W Underflow Interrupt Enable

Enables or disables interrupt requests (TCIU) by the

TCFU flag when the TCFU flag in TSR is set to 1 in

channels 1 and 2.

In channels 0, 3, and 4, bit 5 is reserved. It is always

read as 0 and the write value should always be 0.

0: Interrupt requests (TCIU) by TCFU disabled

1: Interrupt requests (TCIU) by TCFU enabled