Section 20 Controller Area Network

R01UH0134EJ0400 Rev. 4.00 Page 1001 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

TTW[1:0] (Time Trigger Window): These bits show the attribute of time windows. Please

note that once a merged arbitrating window is opened by TTW = 2'b10, the window must be

closed by TTW = 2'b11. Several messages with TTW = 2'b10 may be used within the start and

the end of a merged arbitrating window.

TTW[1] TTW[0] Description

0 0 Exclusive window (initial value)

0 1 Arbitrating window

1 0 Start of merged arbitrating window

1 1 End of merged arbitrating window

The first 16-bit area specifies the time that triggers the transmission of the message in cycle time.

The second 16-bit area specifies the basic cycle in the system matrix where the transmission must

start (Offset) and the frequency for periodic transmission. When the internal TTT register matches

to the CYCTR value, and the internal Offset matches to CCR value transmission is attempted from

the corresponding Mailbox. In order to enable this function, the CMAX (Cycle Maximum

Register) must be set to a value different from 3'b111, the Timer (TCNTR) must be running

(TTCR0 bit15 = 1), the corresponding MBC must be set to 3'b000 and the corresponding TXPR

bit must be set. Once TXPR is set by S/W, this module does not clear the corresponding TXPR bit

(among Mailbox-30 to 24) to carry on performing the periodic transmission. In order to stop the

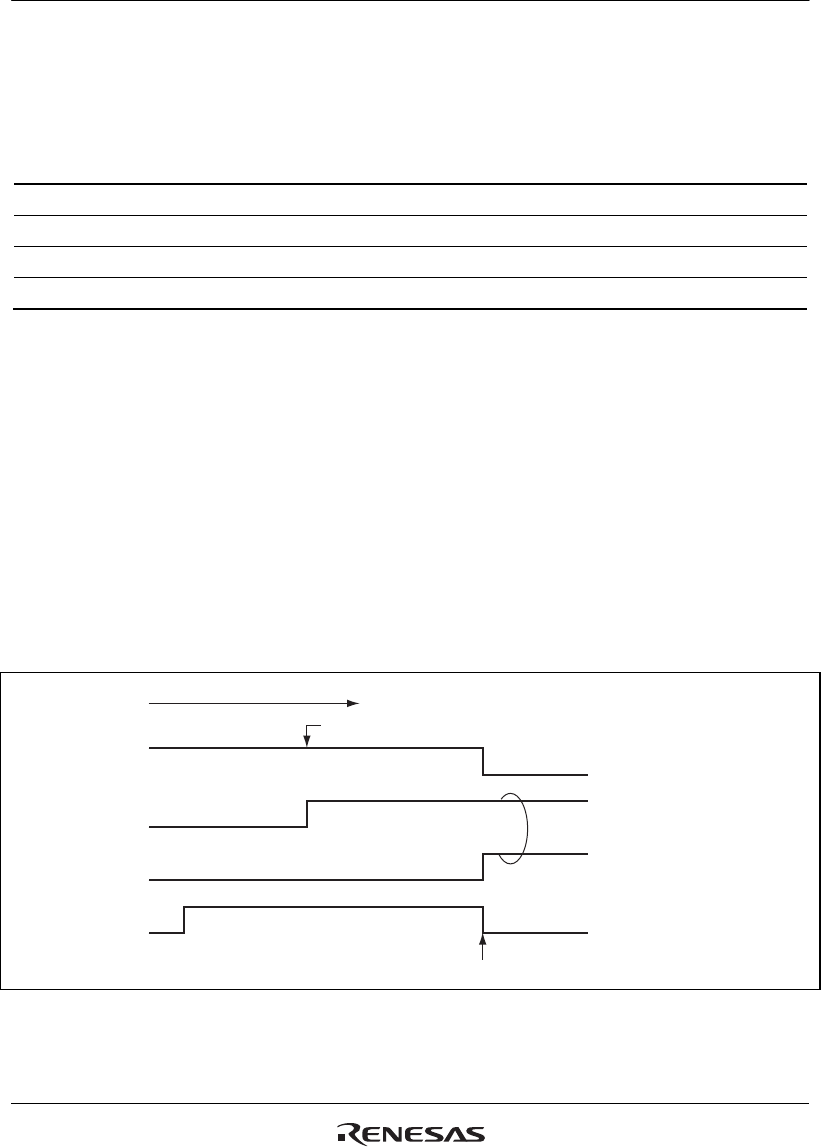

periodic transmission, TXPR must be cleared by TXCR. Please note that in this case it is possible

that both TXACK and ABACK are set for the same Mailbox if TXACK is not cleared right after

completion of transmission. Please refer to figure 20.7.

TXPRI

MBI is under transmission

cancellation is accepted

Both TXACKI and ABACKI

are set without clearing TXACKI

TXPRI is kept set in Time Trigger Mode

TXACKI

ABACKI

TXCRI

Figure 20.7 TXACK and ABACK in Time Trigger Transmission