Section 26 USB 2.0 Host/Function Module

R01UH0134EJ0400 Rev. 4.00 Page 1521 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

(d) Modifying MBW Bits when the Pipe is in the Receiving Direction

When the specified pipe is in the receiving direction, modify the MBW bits in the FIFO port select

registers (CFIFOSEL, D0FIFOSEL, D1FIFOSEL) simultaneously with the CURPIPE bits. When

the DCP is currently set (CURPIPE = 000) in the CFIFO port select register, modify the MBW

bits simultaneously with the CURPIPE bits or ISEL bit.

To modify only the MBW bits for the currently set pipe, follow the procedure below. Once the

buffer memory starts to be read out, however, do not modify the MBW bits until the entire data

has been read out.

When the selected CURPIPE is in the writing direction to buffer memory, the port access width

can be changed simply by setting the MBW bits.

Once the buffer memory starts to be written to, however, do not modify the port access width from

8 bits to 16 or 32 bits, or from16 bits to 32 bits.

When CURPIPE setting is not DCP (000) for D0FIFO, D1FIFO, or CFIFO

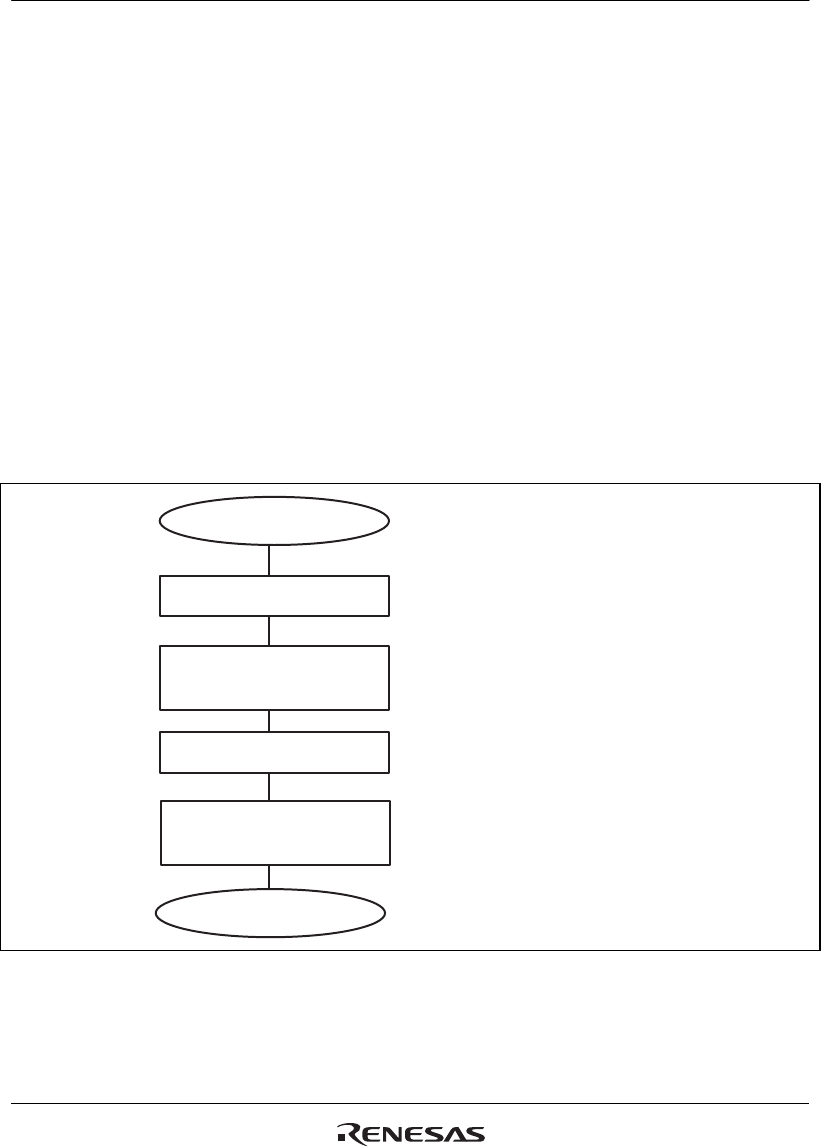

Start

Set CURPIPE to 00.

MBW modification end

[1]

[2]

Read CURPIPE to check that

the read value agrees with

the written value.

Read CURPIPE to check that

the read value agrees with

the written value.

Set MBW and CURPIPE

simultaneously.

[1]

[2]

Set CURPIPE to the value other than

the current value.

Set MBW to any value and set CURPIPE

to the value (pipe) that has been set before

step [1].

Figure 26.14 MBW Modification Procedure Example when CURPIPE Setting is not DCP

(000) for D0FIFO, D1FIFO, or CFIFO