Section 20 Controller Area Network

Page 1054 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

20.4.2 Configuration of This Module

This module is considered in configuration mode or after a H/W (Power On Reset)/S/W (MCR[0])

reset or when in Halt mode. In both conditions this module cannot join the CAN Bus activity and

configuration changes have no impact on the traffic on the CAN Bus.

After a Reset request

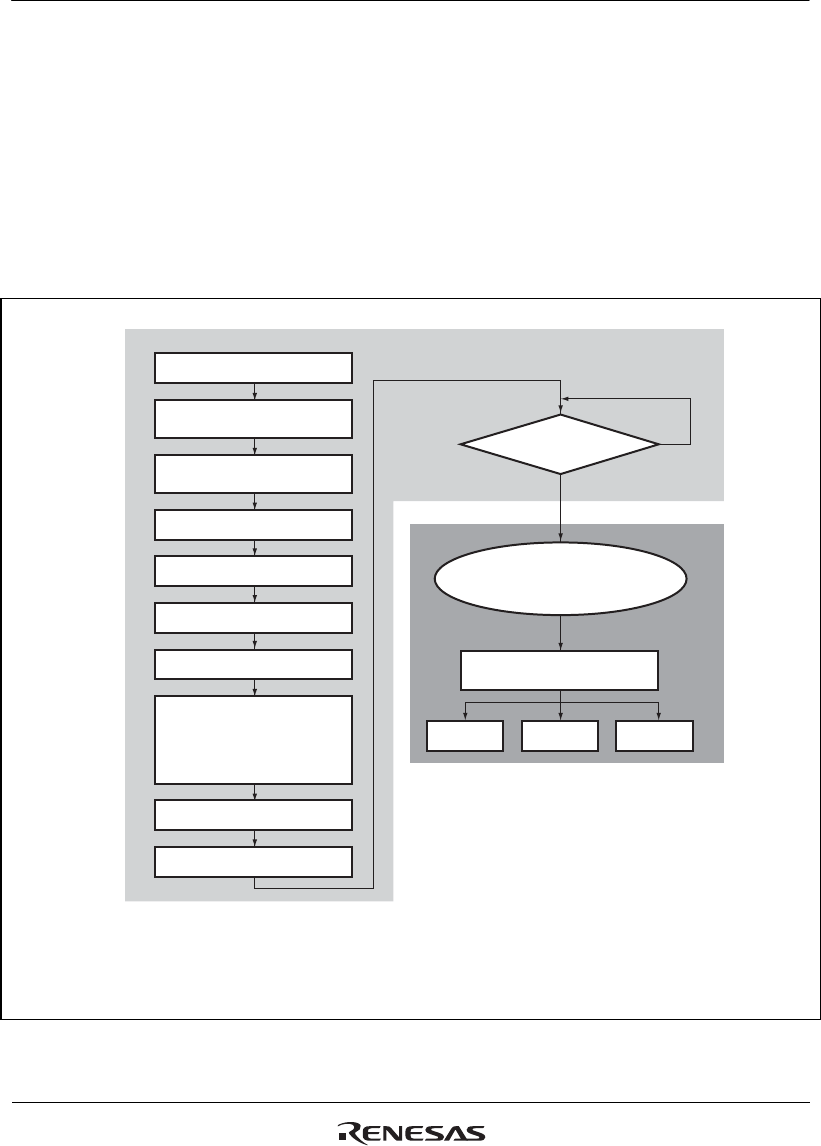

The following sequence must be implemented to configure this module after (S/W or H/W) reset.

After reset, all the registers are initialised, therefore, this module needs to be configured before

joining the CAN bus activity. Please read the notes carefully.

No

Ye s

Power On/SW Reset*

1

Clear IRR[0] Bit

GSR[3] = 0?

Detect 11 recessive bits and

Join the CAN bus activity

RCAN-TL1 is in Tx_Rx Mode

- Set TXPR to start transmission

- or stay idle to receive

Configure MCR[15]

Clear MCR[0]

Clear Required IMR Bits

RCAN-TL1 Timer Reg Setting

Set Bit Timing (BCR)

Mailbox Setting

(STD-ID, EXT-ID, LAFM, DLC,

RTR, IDE, MBC, MBIMR, DART,

ATX, NMC, Tx-Trigger

Time Message-Data)*

2

IRR[0] = 1, GSR[3] = 1

(automatically)

Transmission_Reception

(Tx_Rx) Mode

Receive*

3

Transmit*

3

Timer Start*

4

Notes: 1. SW reset could be performed at any time by setting MCR[0] = 1.

2. Mailboxes are comprised of RAMs, therefore, please initialise all the mailboxes enabled by MBC.

3. If there is no TXPR set, RCAN-TL1 will receive the next incoming message. If there is a TXPR(s)

set, RCAN-TL1 will start transmission of the message and will be arbitrated by the CAN bus.

If it loses the arbitration, it will become a receiver.

4. Timer can be started at any time after the Timer Control regs and Tx-Trigger Time are set.

MCR[0] = 1 (automatically

in hardware reset only)

Configuration Mode

Reset Sequence

Figure 20.14 Reset Sequence