Section 37 Electrical Characteristics

Page 2012 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

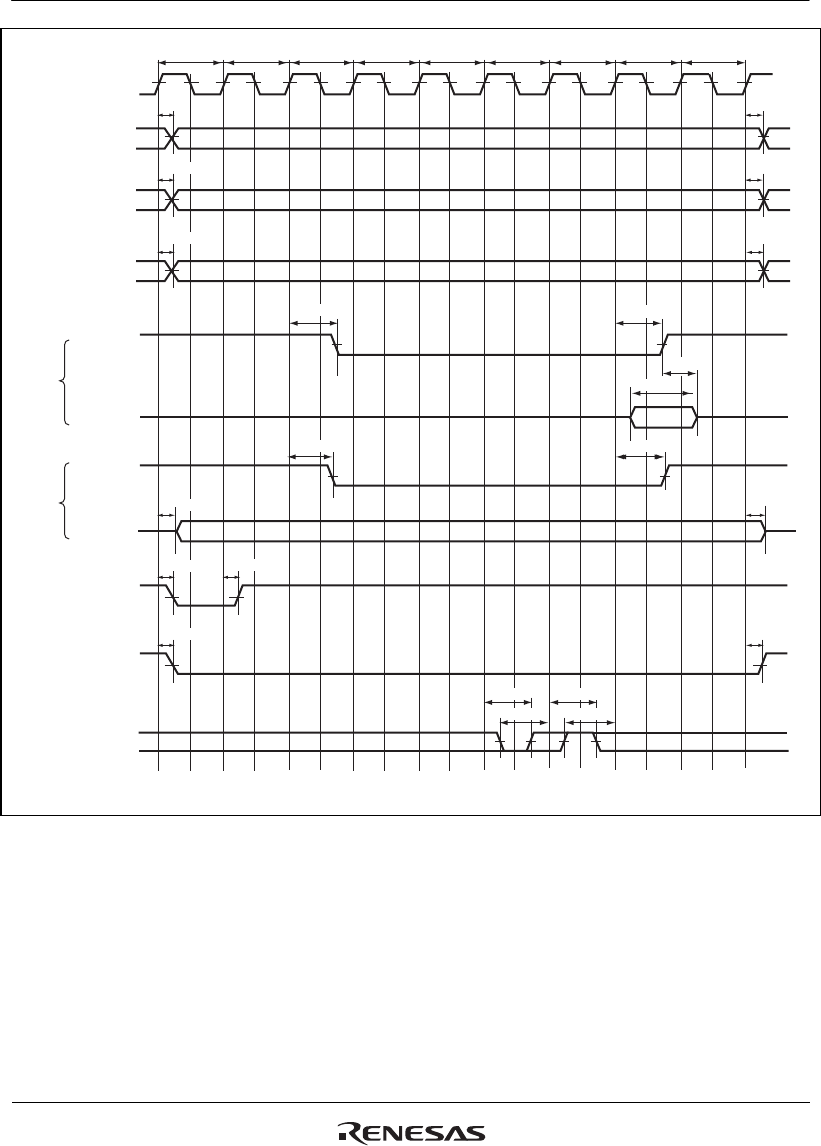

Read

Note: * The waveform for DACKn and TENDn is when active low is specified.

Write

CKIO

A25 to A0

CExx

RD/WR

RD

D15 to D0

WE

D15 to D0

BS

WAIT

t

WTS

t

AD1

t

CSD1

t

RWD1

t

AD1

t

CSD1

t

RWD1

t

BSD

t

BSD

DACKn

TENDn*

t

DACD

t

DACD

t

WDH1

t

WDD1

t

WED1

t

WED1

t

RSD

t

RSD

t

RDH1

t

RDS1

t

WTH

t

WTH

t

WTS

Tpcm1w Tpcm2Tpcm0 Tpcm1 Tpcm1wTpcm0w Tpcm2wTpcm1w Tpcm1w

Figure 37.37 PCMCIA Memory Card Bus Cycle

(TED = 2 Cycles, TEH = 1 Cycle, Software Wait Cycle 0, Hardware Wait Cycle 1)