Section 19 Serial I/O with FIFO

R01UH0134EJ0400 Rev. 4.00 Page 955 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

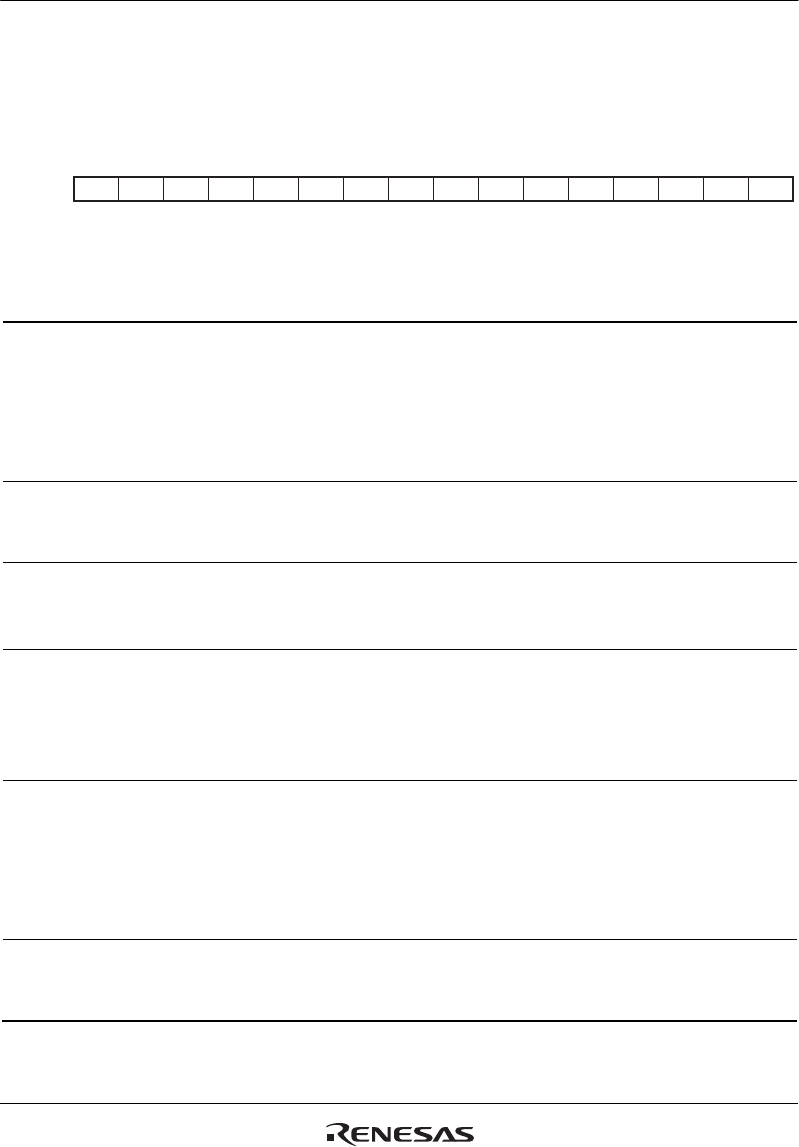

19.3.6 Interrupt Enable Register (SIIER)

SIIER enables the issue of interrupts from this module. When a bit in this register is set to 1 and

the corresponding bit in SISTR is set to 1, this module issues an interrupt.

Bit:

Initial Value:

R/W:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

0000000000000000

R/W R R/W R/W R/W R R/W R/W R R R R/W R/W R/W R/W R/W

TDMAE -

TFEMPE TDREQE

RDMAE -

RFFULE RDREQE

---

FSERRE TFOVFE TFUDFE RFUDFE RFOVFE

Bit Bit Name

Initial

Value R/W Description

15 TDMAE 0 R/W Transmit FIFO DMA Transfer Request Enable

Uses a transmit FIFO transfer request as an interrupt or a

DMA transfer request.

0: Used as an interrupt to the CPU

1: Used as a DMA transfer request to the direct memory

access controller

14 0 R Reserved

This bit is always read as 0. The write value should

always be 0.

13 TFEMPE 0 R/W Transmit FIFO Empty Enable

0: Disables interrupts due to transmit FIFO empty

1: Enables interrupts due to transmit FIFO empty

12 TDREQE 0 R/W Transmit FIFO Transfer Request Enable

0: Disables interrupts/DMA transfer requests due to

transmit FIFO transfer requests

1: Enables interrupts/DMA transfer requests due to

transmit FIFO transfer requests

11 RDMAE 0 R/W Receive FIFO DMA Transfer Request Enable

Uses a receive FIFO transfer request as an interrupt or a

DMA transfer request.

0: Used as a CPU interrupt

1: Used as a DMA transfer request to the direct memory

access controller

10 0 R Reserved

This bit is always read as 0. The write value should

always be 0.