Section 26 USB 2.0 Host/Function Module

R01UH0134EJ0400 Rev. 4.00 Page 1443 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

26.3.36 PIPEn Control Registers (PIPEnCTR) (n = 1 to 9)

PIPEnCTR is a register that is used to confirm the buffer memory status for the corresponding

pipe, change and confirm the data PID sequence bit, determine whether auto response mode is set,

determine whether auto buffer clear mode is set, and set a response PID for PIPE1 to PIPE9. This

register can be set regardless of the pipe selection in PIPESEL.

This register is initialized by a power-on reset. PID[1:0] are initialized by a USB bus reset.

(1) PIPEnCTR (n = 1 to 5)

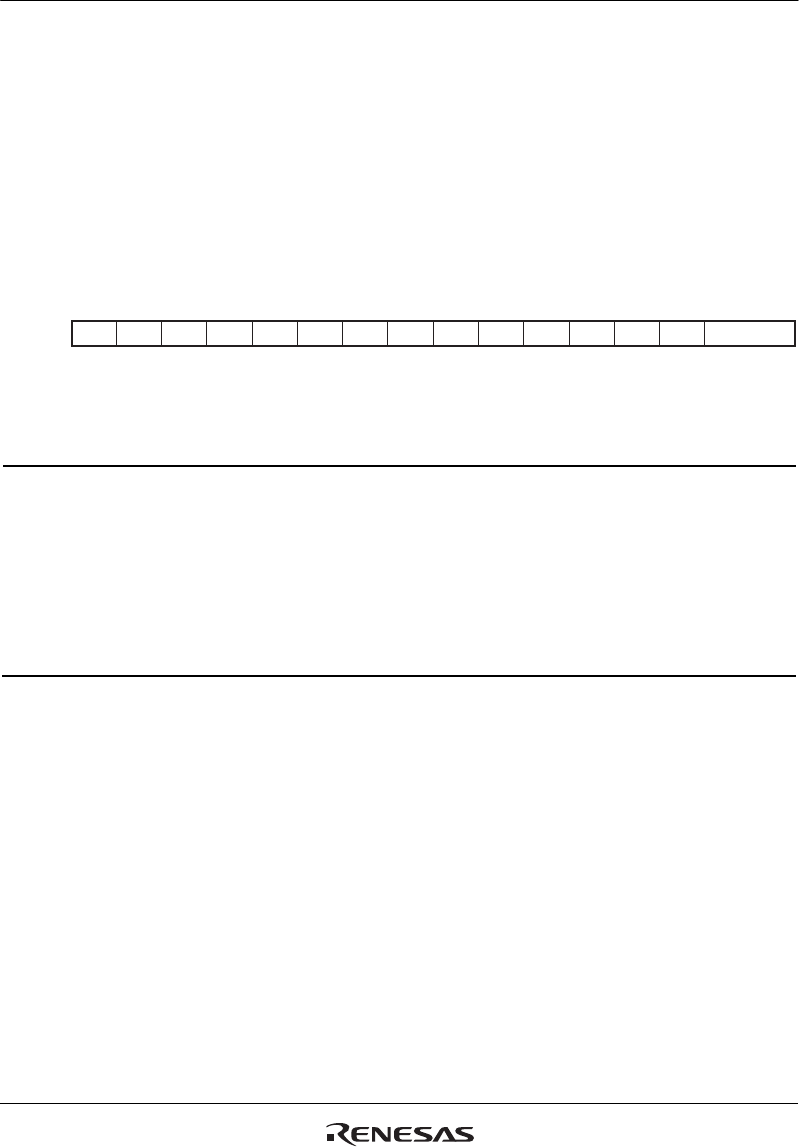

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Bit:

Initial value:

R/W:

0000000000000000

R R R/W* R R R/W R/W R/W* R/W* R R R R R R/W R/W

BSTS INBUFM CSCLR CSSTS —

AT

REPM

ACLRM SQCLR SQSET SQMON PBUSY — — — PID[1:0]

Bit Bit Name

Initial

Value

R/W Description

15 BSTS 0 R Buffer Status

Indicates the FIFO buffer status for the pertinent

pipe.

0: Buffer access is disabled.

1: Buffer access is enabled.

The meaning of this bit depends on the settings of

the DIR, BFRE, and DCLRM bits as shown in table

26.10.