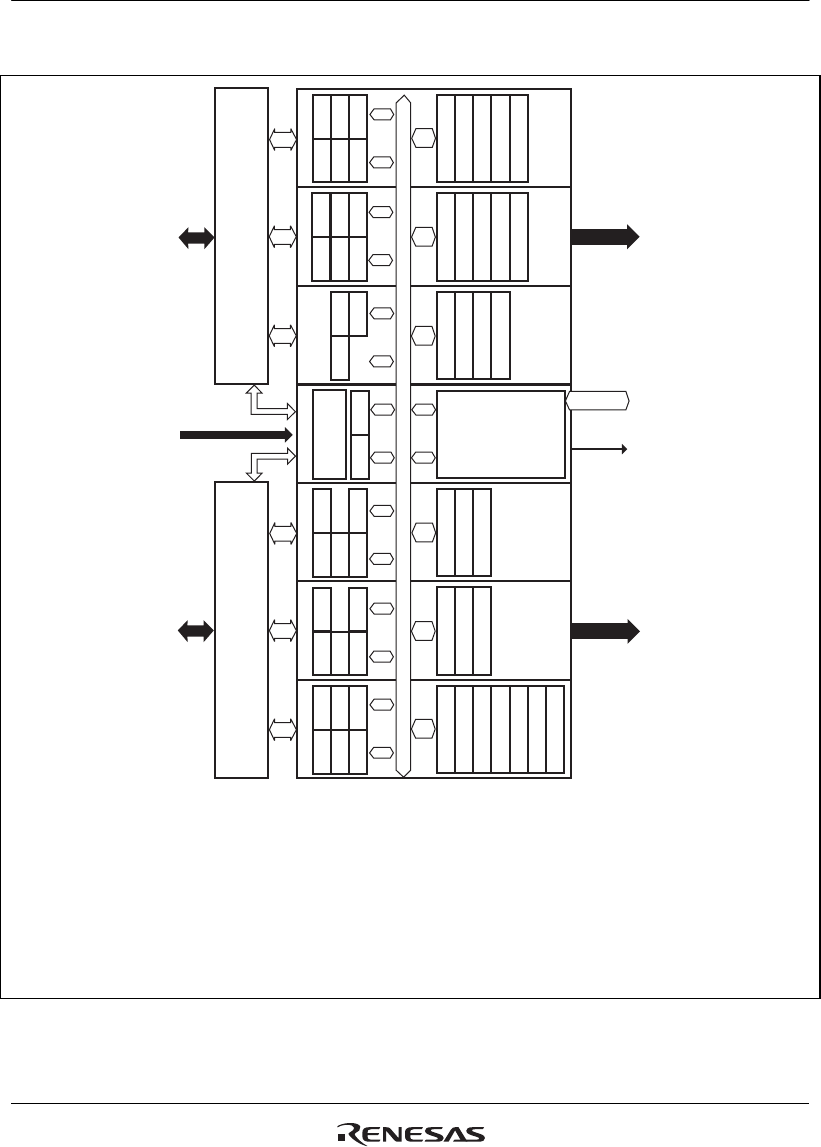

Section 11 Multi-Function Timer Pulse Unit 2

R01UH0134EJ0400 Rev. 4.00 Page 435 of 2108

Sep 24, 2014

SH7262 Group, SH7264 Group

Figure 11.1 shows a block diagram.

TCNT

TGRA

TGRB

TGRC

TGRD

TMDR

TCR

TIORL

TIORH

TSR

TIER

TCNT

TGRA

TGRB

TGRC

TGRD

TMDR

TCR

TIORL

TIORH

TSR

TIER

TCNTS

TCBR

TDDR

TCDR

TOER

TOCR

TGCR

BUS I/F

TCNT

TGRA

TGRB

TMDR

TCR

TIOR

TSR

TIER

TSYR

TSTR

TCNT

TGRA

TGRB

TMDR

TCR

TIOR

TSR

TIER

TCNT

TGRA

TGRB

TGRC

TGRD

TGRE

TGRF

TMDR

TCR

TIORL

TIORH

TSR

TIER

[Legend]

TSTR: Timer start register

TSYR: Timer synchronous register

TCR: Timer control register

TMDR: Timer mode register

TIOR: Timer I/O control register

TIORH: Timer I/O control register H

TIORL: Timer I/O control register L

TIER: Timer interrupt enable register

TGCR: Timer gate control register

TOER: Timer output master enable register

TOCR: Timer output control register

TSR: Timer status register

TCNT: Timer counter

TCNTS: Timer subcounter

TCDR: Timer cycle data register

TCBR: Timer cycle buffer register

TDDR: Timer dead time data register

TGRA: Timer general register A

TGRB: Timer general register B

TGRC: Timer general register C

TGRD: Timer general register D

TGRE: Timer general register E

TGRF: Timer general register F

Clock input

Internal clock: Pφ/1

Pφ/4

Pφ/16

Pφ/64

Pφ/256

Pφ/1024

External clock: TCLKA

TCLKB

TCLKC

TCLKD

Input/output pins

Channel 0: TIOC0A

TIOC0B

TIOC0C

TIOC0D

Channel 1: TIOC1A

TIOC1B

Channel 2: TIOC2A

TIOC2B

Control logic for channels 0 to 2

Interrupt request signals

Channel 0: TGIA_0

TGIB_0

TGIC_0

TGID_0

TGIE_0

TGIF_0

TCIV_0

Channel 1: TGIA_1

TGIB_1

TCIV_1

TCIU_1

Channel 2: TGIA_2

TGIB_2

TCIV_2

TCIU_2

Peripheral bus

A/D converter conversion

start signal

Interrupt request signals

Channel 3: TGIA_3

TGIB_3

TGIC_3

TGID_3

TCIV_3

Channel 4: TGIA_4

TGIB_4

TGIC_4

TGID_4

TCIV_4

Input/output pins

Channel 3: TIOC3A

TIOC3B

TIOC3C

TIOC3D

Channel 4: TIOC4A

TIOC4B

TIOC4C

TIOC4D

Control logic for channels 3 and 4

Control logic

Channel

0 Channel 1 Channel 2

Common

Channel

4 Channel 3

Module data bus

Figure 11.1 Block Diagram