R01UH0134EJ0400 Rev. 4.00 Page 2079 of 2108

Sep 24, 2014

Item Page Revision (See Manual for Details)

22.7.1 Control Register

(CTRL)

1160 Table amended

Bit Bit Name

Initial

Value

R/W Description

3 RCSI 0 R/W Receiver Channel Status Interrupt Enable

Enables the receiver channel status register full interrupts.

0: Receiver channel status interrupt disabled

1: Receiver channel status interrupt enabled

2 RCBI 0 R/W Receiver Channel Buffer Interrupt Enable

Enables the receiver audio channel buffer full interrupts.

0: Receiver audio channel interrupt disabled

1: Receiver audio channel interrupt enabled

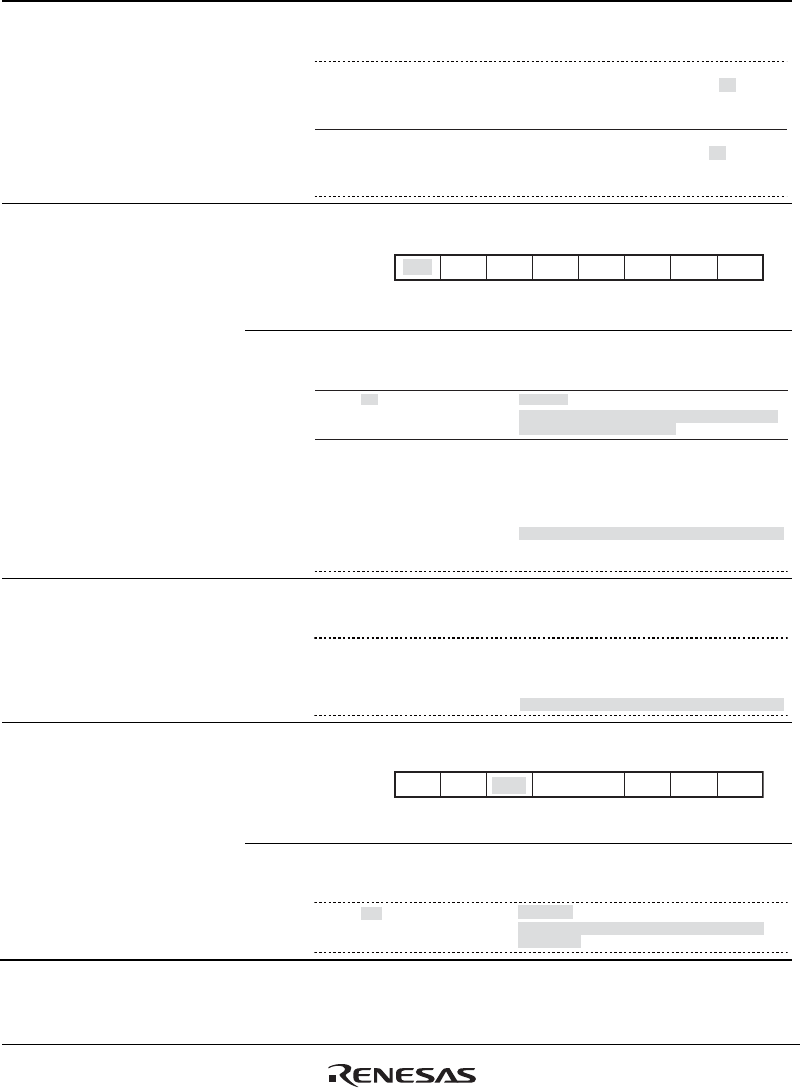

23.3.6 Decoding Option

Setting Control Register

(CROMCTL4)

1206 Figure amended

76543210

00000000

R/W R/W R/W R/W R/W R/W R/W R/W

Bit:

Initial value:

R/W:

-

LINK2

-

ER0SEL NO_ECC

---

1207 Table amended

Bit Bit Name

Initial

Value

R/W Description

7 ⎯ 0 R/W Reserved

The write value may be 0 or 1. When read, this bit has

the value previously written to it.

6 LINK2 0 R/W Link Block Detection Condition

0: The block is regarded as a link block when either run-

out 1 or 2 and both run-in 3 and 4 have been

detected.

1: The block is regarded as a link block when two out of

run-out 1 and 2 and “link” have been detected.

The condition for setting of the LINK_ON bit in

CROMST5 is decoding of the link sector.

23.3.12 Mode

Determination and Link

Sector Detection Status

Register (CROMST5)

1213 Table amended

Bit Bit Name

Initial

Value R/W Description

3

LINK_ON

0 R

This bit is set to 1 when a link block was recognized in

link block determination.

For the criteria for link block determination, refer to the

LINK2 bit in the CROMCTL4 register.

23.3.41 Automatic Buffering

Setting Control Register 0

(CBUFCTL0)

1230 Figure amended

76543210

00000100

R/W R/W R/W R/W R/W R/W R/W R/W

Bit:

Initial value:

R/W:

CBUF_

AUT

CBUF_

EN

-

CBUF_MD[1:0]

CBUF_

TS

CBUF_

Q

-

1231 Table amended

Bit Bit Name

Initial

Value R/W Description

5 ⎯ 0 R/W Reserved

This bit is always read as 0.The write value should

always be 0.