Section 6 Exception Handling

Page 152 of 2108 R01UH0134EJ0400 Rev. 4.00

Sep 24, 2014

SH7262 Group, SH7264 Group

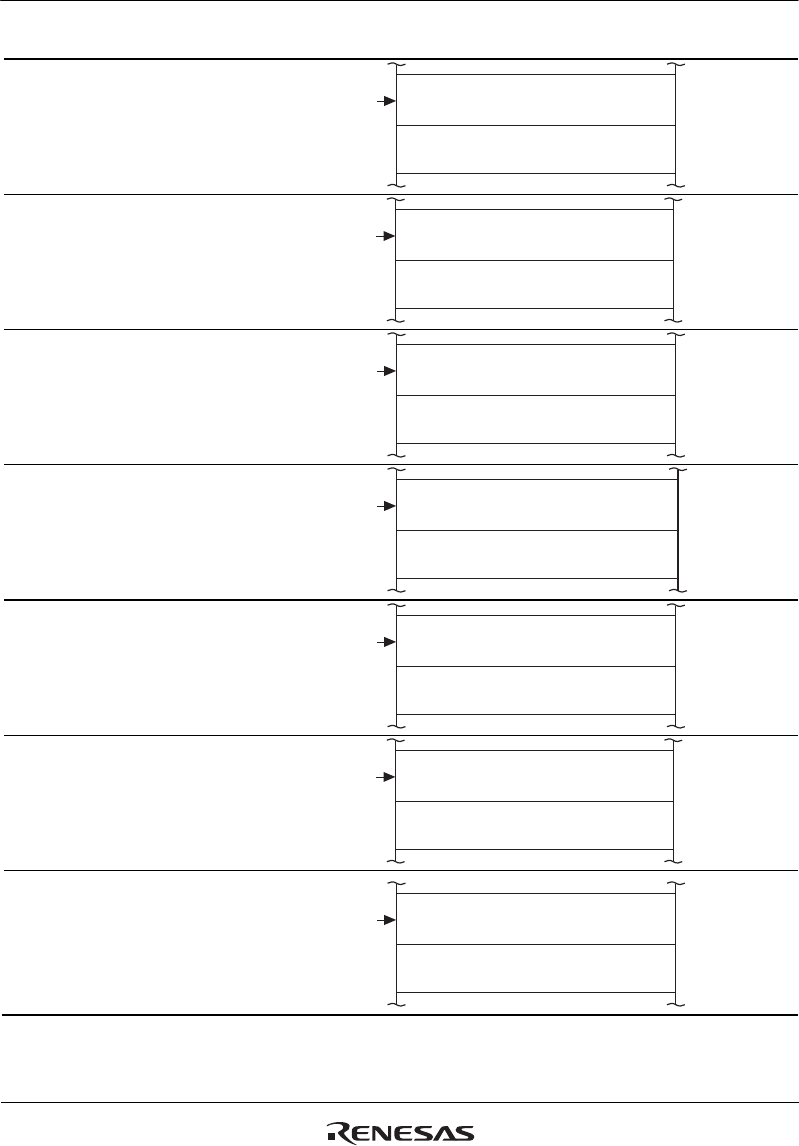

Exception Type Stack Status

Register bank error (overflow)

32 bits

32 bitsSR

Address of instruction

after executed instruction

SP

Register bank error (underflow)

32 bits

32 bitsSR

Start address of relevant

RESBANK instruction

SP

Trap instruction

32 bits

32 bitsSR

Address of instruction

after TRAPA instruction

SP

Slot illegal instruction

32 bits

32 bitsSR

Jump destination address

of delayed branch instruction

SP

General illegal instruction

32 bits

32 bitsSR

Start address of general

illegal instruction

SP

Integer division exception

32 bits

32 bitsSR

Start address of relevant

integer division instruction

SP

FPU exception

32 bits

32 bitsSR

Address of instruction

after executed instruction

SP